## МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

## САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

А.А.АВДЮХИН, Е.В.ДУШУТИНА, А.В.ЖУКОВ

# ИНТЕРФЕЙСЫ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ ЭВМ

Учебное пособие

Санкт-Петербург Издательство СПбГПУ 2011

## МИНИСТЕРСТВООБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

А.А.АВДЮХИН, Е.В.ДУШУТИНА, А.В.ЖУКОВ

# ИНТЕРФЕЙСЫ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ ЭВМ

Учебное пособие

Санкт-Петербург Издательство СПбГПУ 2011 УДК 004.32 (075.8)

Авдюхин А.А., Душутина Е.В., Жуков А.В. Аппаратно-программные средства ввода/вывода: Учеб. пособие. СПб.: Изд-во СПбГПУ, 2011. 153 с.

Учебное пособие соответствует государственному образовательному стандарту дисциплины «ЭВМ и периферийные устройства» базовой части профессионального цикла (направление подготовки 230100 — информатика и вычислительная техника.

Рассмотрены основные принципы, способы и средства обмена информацией между центральной частью ЭВМ и множеством устройств вычислительной системы, которые принято рассматривать как периферийные устройства. Среди этого множества имеются периферийные устройства, знакомые всем по общению с персональными компьютерами, устройства сопряжения с объектами различного назначения, а также «не совсем периферийные» устройства и подсистемы, расположенные в непосредственной близости от центральной части ЭВМ, подключенные к системной шине и участвующие в процессах ввода/вывода информации. Несмотря на значительные различия между этими участниками процессов обмена данными имеется ряд установившихся принципов организации такого обмена, которые положены в основу унифицированных интерфейсов ввода/вывода, на которые направлено главное внимание авторов настоящего пособия.

Учитывая сложившуюся ситуацию на рынке вычислительной техники, большинство примеров в пособии иллюстрирует организацию интерфейсов персональных ЭВМ, построенных на процессорах архитектурного ряда IntelX86...PentiumX. В пособии дается краткое описание основных интерфейсов персональных компьютеров и некоторых функциональных узлов, поддерживающих работу с периферийными устройствами. Во втором и третьем разделах описаны лабораторные работы, которые предлагаются для закрепления лекционного курса.

Пособие предназначено для студентов, проходящих подготовку по направлению 230100, которые изучают на факультете технической кибернетики, кроме упомянутой дисциплины, также курс «Интерфейсы внешних устройств». Это же пособие рекомендуется студентам, обучающимся по направлению 220400 — управление в технических системах, которые изучают дисциплину «Средства сопряжения вычислительных систем с объектом управления»

Табл., Ил., Библиогр.: назв.

Печатается по решению редакционно-издательского совета Санкт-Петербургского государственного политехнического университета.

© Санкт-Петербургский государственный политехнический университет, 2011

## ВВЕДЕНИЕ

Периферийные устройства (ПУ) являются сложными И дорогостоящими изделиями вычислительной техники. Например, если рассмотреть только системный блок современной персональной ЭВМ, то увидим, что на ПУ приходится более 70 % стоимости аппаратных средств, а если учесть другие устройства, необходимые на рабочем месте (монитор, принтер и другие), то получится, что почти вся стоимость комплекса сосредоточена в периферийном оборудовании. Доля программных средств, обеспечивающая работу ПУ, во всем комплексе программного обеспечения ЭВМ также велика. Эффективность вычислительного комплекса в целом в значительной степени определяется организацией работы периферийного оборудования.

Физические принципы, конструктивные особенности периферийных устройств настолько разнообразны, что в рамках короткого курса невозможно подробно рассмотреть эти вопросы. Поэтому целесообразно сделать акцент на изучении интерфейсов. В нашем университете учебный процесс всегда был ориентирован на подготовку инженеров, создающих новую технику. Маловероятно, чтобы наш выпускник занимался разработкой собственно периферийного устройства, такого, как дисплей или принтер. Легче представить, что кому-то придется разрабатывать электронные схемы управления для таких изделий. А вот подключение их к системе, разработка нестандартных контроллеров связи ЭВМ с объектами различного назначения, разработка программных средств управления ими — все это повседневная практика целой армии инженеров. Для успешной работы в этой области необходимо уметь разбираться в технических описаниях как самого объекта, так и интерфейса, с помощью которого этот объект обменивается информацией с ЭВМ. При этом необходимо также иметь ясное представление о физических процессах, протекающих в этих объектах.

Несмотря на значительное разнообразие физических принципов работы ПУ, их подключение к системе и порядок взаимодействия с центральной частью ЭВМ имеет много общего. Это общее, по мнению авторов, должно быть отражено в курсе «ЭВМ и периферийные устройства» и более подробно рассмотрено в курсе «Интерфейсы внешних устройств». Знание основ организации ввода/вывода и, в частности, знакомство с основными интерфейсами позволяет лучше понять особенности вычислительных комплексов и систем.

Системы управления, включающие микропроцессор или компьютер в качестве устройства преобразования, хранения, переработки и представления информации (терминология ГСП — государственной системы промышленных приборов и средств автоматизации), доминируют в технике

систем управления. Поэтому если вычислительная машина (система) предназначена для управления станком, роботом и иными технологическими объектами или процессами, то и в этом случае организация подсистем обмена сигналами с этими объектами обладает первостепенной важностью. При этом подсистемы ввода/вывода имеют много общего с аналогичными подсистемами обычных ЭВМ. Различия обусловлены характером объектов управления (в одном случае это, например, принтер, а в другом — роботштабелер на автоматизированном складе).

Наиболее распространенными и доступными ЭВМ в настоящее время являются персональные ЭВМ, построенные на процессорах ряда Intel 8X86... Pentium X и их аналогах, которые для краткости называют IBM/PC или просто PC (персональный компьютер — ПК). Поэтому в качестве примеров использованы интерфейсы и контроллеры, применяемые в этих системах. Это тем более оправдано, что по тем же стандартам выполнены ЭВМ других классов, например, управляющие (индустриальные) ЭВМ, промышленные программируемые контроллеры и др.

В предлагаемом пособии содержится изложение общих принципов обмена информацией в ЭВМ, дается краткое описание основных интерфейсов персональных компьютеров и некоторых функциональных узлов, поддерживающих работу с периферийными устройствами.

Пособие предназначено для студентов, проходящих подготовку по направлению 230100 (информатика и вычислительная техникаё), которые изучают на факультете технической кибернетики курс «ЭВМ и периферийные устройства», а также курс «Интерфейсы внешних устройств». Это же пособие рекомендуется студентам, обучающимся по направлению 220400 (управление в технических системах), которые изучают дисциплину «Средства сопряжения вычислительных систем с объектом управления»

В последние годы по данной тематике для поддержки лабораторных работ были изданы учебные пособия [1, 2], тиражи которых повторялись. Настоящее издание представляет собой переработанное объединение указанных пособий, выполненное на основании опыта проведения занятий со студентами 3...4 курсов.

Для усвоения материала пособия студенты должны иметь достаточную подготовку по информатике и микросхемотехнике. Желательно иметь навыки программирования на языке ассемблера.

Пособие состоит из трех разделов. В первом — изложены общие вопросы организации обмена информацией в ЭВМ, описаны некоторые интерфейсы, характерные для персональных компьютеров. Эти материалы можно использовать для подготовки к экзамену по теоретической части курса.

Во втором разделе описаны лабораторные работы, которые предлагаются для закрепления лекционного курса. Первые две работы,

посвященные работе с регистрами ПУ вручную и в автоматическом режиме по опросу готовности и в режиме прерывания, являются вводными работами и выполняются всей группой одновременно. Для выполнения этих работ не требуется специального оборудования, и они могут выполняться на любых рабочих местах. Остальные работы для своего выполнения требуют, как правило, дополнительных устройств, не входящих в стандартный комплект ПК. Поэтому они выполняются по графику.

В третьем разделе предлагаются лабораторные работы, направленные на освоение традиционной системы прерываний, реализованной в архитектуре персональных компьютерах и в аналогичных по архитектуре управляющих ЭВМ.

Все работы рассчитаны на индивидуальное выполнение в течение четырех академических часов. Для успешного выполнения работ требуется домашняя подготовка по заданию, полученному на предыдущем посещении. Предполагается, что выполняющие работу студенты освоили приемы программирования и отладки программ на языке ассемблера (А86 или TASM).

Работы завершаются оформлением отчета, в котором должны быть представлены следующие материалы:

- цели работы,

- укрупненная функциональная схема исследуемого объекта (или графическое представление программной модели),

- формулировка задания,

- тексты отлаженных программ с комментариями,

- если требуется, временные диаграммы с оцифровкой осей,

- содержательные выводы по проделанной работе.

# 1. ОБЩАЯ ХАРАКТЕРИСТИКА ИНТЕРФЕЙСОВ ПЭВМ

## 1.1. Основные термины. Классификация интерфейсов

При рассмотрении проблем, связанных со взаимодействием элементов систем обработки информации, систем передачи данных и иных систем, построенных на основе вычислительных машин, используется ряд понятий и соответствующих терминов. Некоторые из них приведены в этом параграфе. Следует иметь в виду, что в различных литературных источниках можно встретить различающиеся толкования одинаковых терминов.

**Интерфейс**. Одно из центральных понятий. Существует целый ряд его определений, в том числе закрепленных ГОСТ ами. Упрощенно интерфейс можно определить как совокупность средств и правил, обеспечивающих взаимодействие компонентов вычислительной системы или сети. Под средствами понимается как аппаратура, так и программно-алгоритмическое обеспечение.

**Протокол.** Понятие, обозначающее совокупность правил, алгоритм взаимодействия устройств, подсистем или специалистов при реализации определенных функций (в нашем случае — при обмене информацией).

**Линия интерфейса.** Техническая («в металле») реализация интерфейса представляется как совокупность линий интерфейса (обычно это электрические проводники) с элементами подключения к устройствам, между которыми устанавливается связь.

**Шина**. Это совокупность линий, сгруппированных по функциональному признаку (шина данных, шина адреса и др.). Иногда шиной называют совокупность всех линий интерфейса. В этом же смысле употребляется термин **магистраль**. Обычно, когда говорят о шине или магистрали, то предполагают, что они допускают параллельное подключение к ним нескольких устройств, обменивающихся информацией. Т.е. линии шины являются линиями коллективного пользования.

**Канал.** Этим термином обозначается среда распространения сигналов, что соответствует интуитивному пониманию. Однако термины **канал связи** или **канал передачи данных** охватывают кроме среды еще и аппаратуру, обеспечивающую связь или передачу данных. В вычислительной технике существуют **каналы ввода-вывода,** под которыми понимаются устройства (часто это специализированные ЭВМ), обеспечивающие передачу данных между основной памятью и периферийными устройствами.

**Контроллер.** Это общий термин для обозначения устройств управления. Когда речь идет об интерфейсах, то под контроллерами понимаются устройства управления внешними или периферийными устройствами. Часто их называют контроллерами ввода/вывода. В

повседневной практике для контроллеров разных периферийных устройств закрепились разные наименования, например, карта, адаптер и некоторые другие, но по сути дела все это контроллеры.

В соответствии с ГОСТ 26.016—81 установлено четыре **основных** классификационных признака интерфейсов [3]:

- способ соединения компонентов (магистральный, радиальный, цепочечный, смешанный),

- способ передачи информации (параллельный, последовательный, параллельно-последовательный),

- принцип обмена информацией (асинхронный, синхронный, изохронный (цикл обмена повторяется через равные промежутки времени)),

- режим передачи информации (двухсторонняя одновременная, то же поочередная, односторонняя).

Имеется ряд других классификационных признаков, более полно характеризующих интерфейсы (функциональное назначение, логическая организация, функциональная организация, физическая реализация и др.). Отметим классы по функциональному назначению:

- системные (машинные или ввода/вывода) интерфейсы ЭВМ,

- сосредоточенных магистральных мультипроцессорных систем,

- периферийного оборудования (общего назначения и специализированные),

- сетей передачи данных,

- модульных систем и приборов,

- локальных вычислительных сетей (ЛВС),

- распределенных систем (в том числе управления).

Эти классы можно бы укрупнить: машинные, периферийного оборудования и сетевые.

# 1.2. Принципы взаимодействия устройств на шине.

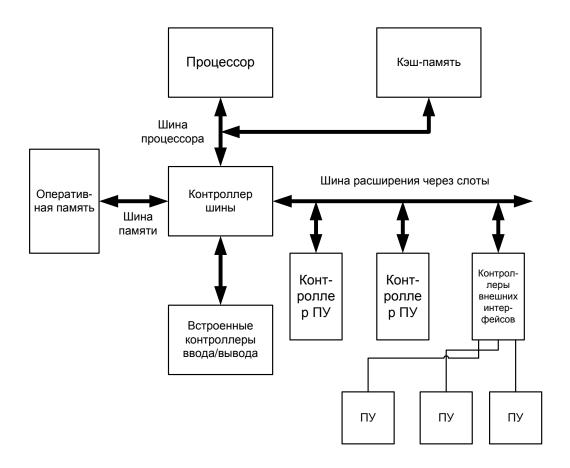

Устройства (компоненты) ЭВМ обмениваются между собой информацией при помощи системы шин. Обычно ЭВМ содержит шины процессора, памяти, ввода-вывода и, возможно, ряд других. Представление о составе ЭВМ и системе ее шин дает структурная схема (рис.1.1). Шины, показанные на этом рисунке, являются шинами межмодульного обмена. В них используется параллельный способ передачи основной информации. На физическом уровне элементарный акт взаимодействия устройств на шине сводится к установлению на линиях шины потенциалов стандартного уровня.

Рис.1.1. Система шин ЭВМ

Передача информации между устройствами ЭВМ является по существу межрегистровой передачей, знакомой студентам из курса схемотехники. Описание работы шины обычно ведется от имени «наблюдателя», находящегося в устройстве, осуществляющем управление процессом обмена. Часто в этой роли выступает центральный процессор ЭВМ.

Таким образом, на шине возможны такие виды взаимодействия устройств как чтение и запись. Например, чтением является передача информации из ячейки памяти или регистра контроллера ПУ в один из регистров процессора при выполнении команды чтения. Записью является передача информации в противоположном направлении.

Можно указать еще на один вид взаимодействия устройств на шине. Это установка управляющих сигналов, обеспечивающих вход в прерывание, в режим прямого доступа к памяти или в режим захвата шины и выход из этих режимов. Сама по себе работа в режимах прерывания, прямого доступа или захвата шины является по существу последовательностью передач информации типа чтение и запись.

Организация системного магистрального интерфейса и обмен информацией на шине основывается на ряде принципов, которые являются общими для всех шин.

Принцип подчиненности («ведущий-ведомый») заключается в том, что при взаимодействии устройств одно из них играет роль ведущего, управляя всем ходом обмена информации, а другое (или несколько других) являются подчиненными. В разных стандартах для понятий ведущий и ведомый используются разные термины. Так в шине Q-BUS это активное и пассивное устройства, в шине ISA это задатчик и исполнитель, в шине PCI это инициатор и цель. Термины «задатчик» и «исполнитель» являются стандартными и рекомендуются для использования в технической документации.

**Принцип квитирования** («запрос-ответ») заключается в том, что в определенных ситуациях продолжение цикла взаимодействия зависит от наличия ответного сигнала (quit) от ведомого устройства. Использование ответного сигнала придает обмену асинхронный характер, позволяет надежно и без излишних временных затрат осуществлять обмен информацией с устройствами различного быстродействия.

**Принцип унификации** состоит в обеспечении информационной, электрической и конструктивной совместимости компонентов вычислительной системы.

Информационная совместимость [3] ЭТО согласованность функциональных элементов вычислительной системы в взаимодействия соответствии с логическими условиями. Логические условия определяют структуру и состав шины, порядок взаимодействия устройств в различных режимах работы интерфейса, кодирование и форматы команд, данных, адресов и информации состояния устройств, причинно-следственные связи и временные соотношения между сигналами управления. Т.е. логические совместимости условия информационной определяют функциональную и структурную организацию интерфейса и сложность схемотехники и программного обеспечения интерфейса.

Электрическая совместимость — это согласованность параметров электрических сигналов в линиях интерфейса. Ограничения налагаются как на статические параметры (уровни сигналов), так и на динамические (длительности фронтов, задержки). При этом учитывается техническая реализация устройств, взаимодействующих на шине, т.е. потребление энергии во входных цепях и нагрузочная способность выходных каскадов элементов, задержки распространения сигнала. Учитывается также пространственное размещение устройств, так как от этого зависят электрические параметры сигналов.

Конструктивная совместимость — это согласованность конструктивных параметров изделий, входящих в состав интерфейса, предназначенных для механического их соединения. Унификация распространяется на типы соединителей (вилки и розетки, которые в повседневном общении чаще называют разъемами), конструкции плат, каркасов, стоек и т.п. Обычно

требования к конструктивным параметрам являются важной составной частью спецификации (описания) интерфейса.

Контроллеры ввода/вывода. К основным принципам организации магистральных интерфейсов (шин) следует отнести также применение контроллеров ввода/вывода — устройств, с помощью которых центральная ЭВМ через шину связана с периферийными устройствами. Контроллеры в своем составе имеют регистры, через которые и передается информация. Эти регистры часто называют регистрами ввода/вывода. производится по адресам адресного пространства Обращение к ним ввода/вывода. В некоторых архитектурах адресные пространства основной памяти и ввода/вывода объединены. Через эти регистры осуществляется чтение/запись данных, управление периферийным устройством, а также проверка его состояния. Соответственно указанные регистры называются регистрами данных, управления и состояния.

В практике последних лет за регистрами ввода/вывода закрепилось наименование «порты». Происхождение этого термина связано с традиционным его употреблением для обозначения аппаратуры сопряжения шины с устройством ввода-вывода. Для программиста операции записи в порт или чтения порта сводились к обращению по соответствующему адресу, поэтому регистры контроллера естественно отождествлялись с портами ввода/вывода.

Адресные пространства ввода/вывода и основной памяти могут быть объединенными или раздельными. Примером единого адресного пространства является межмодульный параллельный интерфейс (МПИ) [3]. Для регистров ввода/вывода там отведено 8К старших адресов адресного пространства. При этом команды чтения/записи этих регистров не отличаются от соответствующих команд обращения к памяти по записи их в тексте программы. Состав управляющих сигналов, которыми обмениваются устройства на шине при обмене с памятью и ПУ при выполнении этих команд, и временные диаграммы имеют лишь небольшие отличия.

Примерами разделенных адресных пространств памяти и ввода/вывода являются адресные пространства шин ISA и PCI, которые рассмотрены в последующих разделах настоящего пособия. В системе команд микропроцессоров, поддерживающих обмен информацией по этим шинам, для обращения к портам имеются специальные команды In (input, т.е. чтение или ввод) и Out (output, т.е. запись или вывод). Циклы ввода/вывода (временные диаграммы формирования сигналов на линиях шины при выполнении этих команд) отличаются от циклов обращения к памяти как по временным характеристикам, так и по составу управляющих сигналов на линиях шины, что и обеспечивает разделение адресных пространств.

Процессор и периферийные устройства работают относительно независимо, а главное, в разном темпе. Для успешной передачи информации между ними необходимо, чтобы шина была свободна, а участники обмена

были готовы. Избежать потерь информации при обмене помогает использование следующих режимов или видов обмена:

- режим программного опроса готовности,

- режим прерывания,

- режим прямого доступа к памяти (ПДП), а также похожий на него режим захвата шины.

В режиме программного опроса готовности по программе периодически опрашивается регистр состояния ПУ, в котором содержится информация о готовности его к обмену. При выявлении готовности устройства процессор по программе выполняет требуемое действие (чтение или запись).

Ниже приведен пример фрагмента программы на языке ассемблера, в котором в режиме опроса готовности производится обмен информацией с ПУ. В скобки заключены команды, относящиеся только к записи. Предполагается, ЧТО устройство, ИЗ которого читается (в записывается) информация, имеет регистр состояния (порт) с адресом status и регистр данных с адресом buf. В регистре состояния разряд п несет информацию о готовности к чтению (записи). Значение bit n = 1 свидетельствует о готовности устройства. Напомним, что команды in и out работают так, что обмен производится через регистр al/ax процессора, адрес порта задается либо в регистре dx, либо, если адрес не больше 0ff, непосредственно в самой инструкции.

```

; адрес регистра состояния в dx

mov dx, status

metka:

al, dx

; чтение регистра состояния

test al, bit n

; если устройство не готово, то

; продолжить опрос

jz metka

; подготовка к выводу байта из bl)

(mov

al, bl

mov dx, buf

; адрес регистра данных - в dx

; чтение данных из ПУ

in

al, dx

(out dx, al

; запись

данных в ПУ)

```

В результате выполнения этого фрагмента байт из порта **buf** окажется в регистре **al** (в случае вывода байт из регистра **bl** будет записан в порт **buf**). Таким образом, в режиме опроса готовности инициатором обмена является программа, а управление обменом осуществляется также программой.

Обмен в режиме прерывания производится по программе, которая выполняется по запросу от периферийного устройства. При этом процессор выполняет свою основную работу, не теряя времени на постоянные обращения к регистрам состояния своих ПУ. В целом схема взаимодействия

ПУ и центральной части ЭВМ выглядит следующим образом. Периферийное устройство выставляет сигнал запроса, который, в конечном счете, поступает на вход процессора. Последний, если прерывания не запрещены, заканчивает какие-то действия, которые нельзя прерывать (например, выполняет текущую команду до полного завершения, чтобы избежать потери данных), а затем, позаботившись о сохранении необходимых для возврата данных, переходит на выполнение той программы, которую требует ПУ. Эта программа называется программой обработки запроса на прерывание или просто обработчиком. Этот обработчик и выполняет необходимые действия по обмену информацией. Более подробно организация работы ЭВМ при входе в прерывание будут рассмотрена в п.1.4. Таким образом, инициатором обмена в режиме прерывания является ПУ, а управляет обменом — программа, но не основная, а специально заготовленная для обработки запроса на прерывание (обработчик).

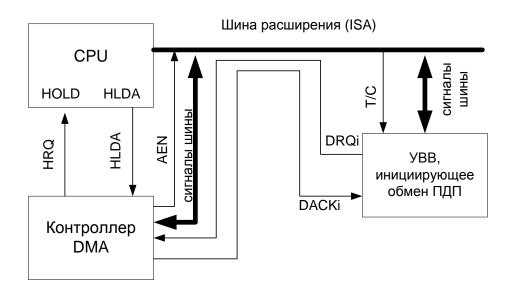

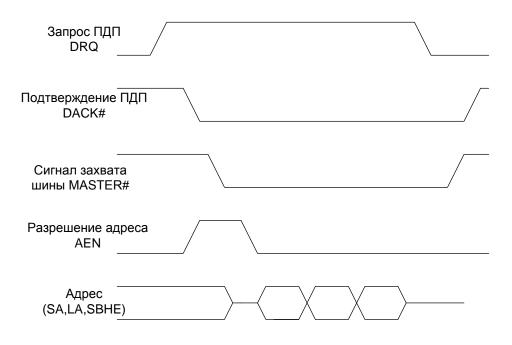

Обмен информацией в режиме прямого доступа к памяти (ПДП) выполняется также по запросу от ПУ, но, в отличие от режима прерывания, управление обменом осуществляет не центральный процессор, а специальный контроллер ПДП, который формирует все необходимые для обмена сигналы. При этом центральный процессор находится в пассивном состоянии до окончания цикла ПДП. В буквальном смысле ПДП — это обмен данными между памятью и периферийным устройством, этим обменом и управляет контроллер ПДП. Во многих стандартах существует режим очень похожий на ПДП, который называется режимом прямого управления шиной или режимом захвата шины. В этом режиме устройство, выставившее запрос, после получения разрешения от задатчика (владельца шины) само становится задатчиком и управляет всеми процессами, управляя обменом (не обязательно с памятью).

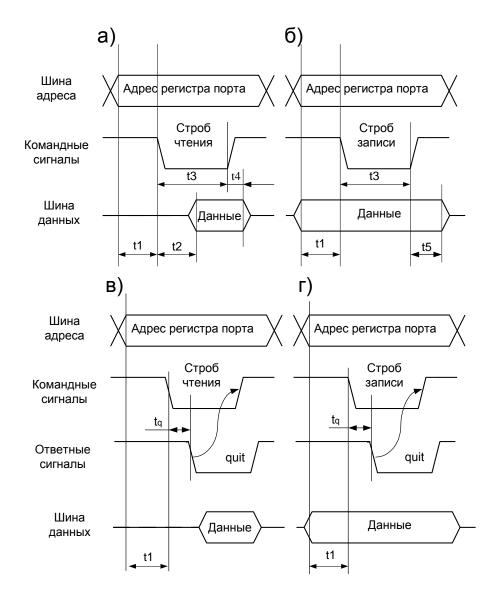

Собственно передача информации на физическом уровне сводится к установлению на линиях шины в соответствии с принятым протоколом информационных и управляющих сигналов. Для всех шин характерна следующая последовательность действий (рис. 1.2). Ведущее устройство устанавливает адресные сигналы на шине адреса. Затем с достаточной для распознавания «своего» адреса ведомыми устройствами задержкой ведущее устанавливает командные сигналы на шине управления. Ведомое устройство за время t1 распознает факт обращения к себе, в случае надобности выдает ответные сигналы через время tq. Если выполняется чтение, то с задержкой свойствами, определяемой внутренними ведомое устройство сигналы на шине данных, которые фиксируются во устанавливает внутренних регистрах ведущего устройства. Если выполняется запись, то ведущее устройство помещает сигналы на шине данных, которые под действием командных сигналов записываются в регистры ведомого устройства.

В простых интерфейсах прошлых поколений командные сигналы по шине управления передавались непосредственно в виде управляющих сигналов, таких как стробы чтения или записи. При этом фиксация информации на принимающей стороне производится по спаду строба. Для цикла чтения устанавливается ограничение сверху на время t4 удержания ведомым устройством данных на шине после снятия строба: шина данных должна быть освобождена для следующего цикла. Для цикла записи устанавливается ограничение снизу для времени t5 удержания ведущим устройством данных на шине для надежности записи.

Рис.1.2. Временные диаграммы чтения/записи: а — синхронный цикл чтения; б — синхронный цикл записи; в — асинхронный цикл чтения; г — асинхронный цикл записи

При синхронном обмене длительности стробов (t3) являются фиксированными. При асинхронном обмене t3 зависит от момента прихода ответного сигнала: строб снимается только после получения ведущим устройством сигнала quit. Время tq определяется быстродействием ведомого устройства. Отсутствие ответа в течение заданного максимума расценивается как сбой в работе шины. В работе большинства шин, нашедших практическое применение, сочетаются синхронный и асинхронный принципы.

## 1.3. Шины расширения ЭВМ

#### 1.3.1. Системные интерфейсы и шины расширения

Интерфейсы, предназначенные для обмена информацией между центральным процессором и основными устройствами ЭВМ, получили название системных интерфейсов или шин. По другому определению системной шиной считается та, через которую передается основной объем информации в ЭВМ. Системный интерфейс во многом определяет архитектуру ЭВМ в целом. В современных ЭВМ, в частности, в ПЭВМ, понятие системной шины оказывается размытым из-за того, что для повышения производительности целый ряд устройств подключается с помощью локальных шин. Например, видеоподсистема современных ПЭВМ подключена к процессору с помощью параллельного интерфейса AGP. Несколько ранее для этой цели широко использовалась локальная шина VL-bus. Для обеспечения работы современных дисплеев в графическом режиме по этим шинам передается гигантский объем информации. Для подключения внешних накопителей и ряда других устройств используются интерфейсы SCSI или ATA, которые организованы по принципу шины. Таким образом, система шин ЭВМ является сложной многоярусной и шина, которая ранее считалась бы системной, оказывается лишь одной из нескольких. Вероятно поэтому в последнее время шину, через периферийных подключаются контроллеры устройств, которую требующих особо высокой производительности обмена информацией, называют шиной ввода/вывода или шиной расширения. Примерами таких шин являются шины Q-bus, ISA, VME, EISA, MCA, PCI и целый ряд других.

#### 1.3.2. Краткая характеристика шины ISA

Шина ISA (Industrial Standart Architecture) была разработана для персональных ЭВМ типа IBM PC AT и первоначально использовалась в

шины и сохранилась в современных ПЭВМ для качестве системной подключения контроллеров или плат расширения широкой номенклатуры. ЭВМ, использующих эту шину, классом является промышленных или индустриальных ПЭВМ, имеющих в своем составе разнообразные и часто нестандартные платы сопряжения с объектом управления. Существует также шина РС-104, логически эквивалентная шине ISA, применяемая в управляющих микро-ЭВМ [5]. Фактически шина ISA стала стандартом для производителей персональной и индустриальной вычислительной техники, хотя в литературе отмечается, что этот факт не закреплен в официальных документах и это приводит к существованию различий в конкретных образцах продукции разных фирм. Здесь, однако, будем называть общедоступные сведения об этой шине [3...5] стандартом.

Шина ISA имеет раздельные линии (шины) адреса и данных. Разрядность шины данных равна 16, но обмен может осуществляться и 8-разрядными порциями (байтами). Адрес имеет разрядность до 24 при обращении к памяти. Для адресации устройств ввода/вывода может использоваться 16 адресных линий, но практически используется только десять. В стандарте ISA ведущее устройство называется задатчиком, а ведомое — исполнителем. На магистрали присутствуют следующие устройства, способные быть задатчиками:

- центральный процессор,

- контроллер прямого доступа к памяти (ПДП),

- контроллер регенерации памяти,

- периферийная плата.

Первые три устройства расположены на системной или материнской плате (для ПЭВМ обычного исполнения). Кроме них на материнской плате имеется ряд устройств, которые не могут быть задатчиками, но взаимодействуют с шиной (часы реального времени, таймер-счетчик, «кросс», основная память, контроллер прерываний, перестановщик байтов, ряд устройств ввода-вывода). В литературе по шине ISA все перечисленные устройства называются ресурсами.

Магистраль может работать в четырёх основных режимах, называемых циклами:

- доступ к ресурсу (обращение центрального процессора или периферийной платы на шине, к другому ресурсу на шине),

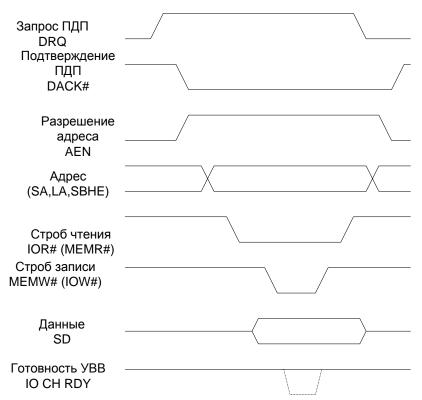

- прямой доступ к памяти ПДП (обмен данными между памятью и устройством на шине, получившим это право, под управлением контроллера ПДП, который является задатчиком на шине),

- регенерация (регенерация динамической памяти ЭВМ под управлением контроллера регенерации),

- захват шины (выполняется периферийной платой для того, чтобы стать задатчиком на шине).

Основные режимы имеют по несколько реализаций в зависимости от типа устройств, обменивающихся информацией (см. п. 1.3.4).

#### 1.3.3. Сигналы шины ISA

Рассмотрим состав шины по группам сигналов с самыми краткими пояснениями. Для получения более подробной информации, необходимой, например, при выполнении курсового проекта, следует обратиться к литературе [3...5].

В магистрали ISA используется положительная логика. Символ «-» (минус) перед обозначением сигнала указывает на то, что данный сигнал имеет активное (в терминах описания шины ISA «разрешенное») состояние при низком потенциале на соответствующей линии. Циклы на шине ISA выполняются по-разному в зависимости от типа ресурса, который распознается задатчиком по ответным сигналам от исполнителя.

#### Адресные сигналы

Это две группы линий. SA0...SA19 — фиксируемые адресные разряды (действительны в течение всего цикла обмена) и LA17...LA23 — нефиксируемые адресные разряды (действительны только в начале цикла обмена).

При обращении к памяти SA0...SA19 это 20 младших разряда адреса. При обращении к УВВ действительны только SA0...SA15, но большинство реальных плат работают только с SA0...SA9. Многие из адресов адресного пространства УВВ закреплены за конкретными устройствами ЭВМ. Резервными являются адреса 360h...36Fh. В адресном пространстве памяти также имеется ряд областей для специальных целей [6].

LA17...LA23 использовались для адресации добавочной памяти, подключенной через слоты ISA. В моделях последних лет платы памяти подключаются иным способом (см. рис.1.1), и данные адресные линии практически не используются.

К этой же группе относятся еще три сигнала.

-SBHE (System Bus High Enable) - разрешение байта, определяет тип цикла (8- или 16-разрядный).

BALE (Bus Address Latch Enable) — сигнал стробирования адресных разрядов. Использовался для фиксации LA17...LA23. Может использоваться в УВВ, но применяется редко.

AEN (Address Enable) — разрешение адреса. В режиме ПДП сообщает всем устройствам, что выполняется цикл ПДП, т.е. на адресной шине установлен адрес памяти, поэтому периферийные устройства не должны на этот адрес реагировать.

#### Шина данных

SD0...SD15 — разряды данных.

#### Командные сигналы

Сюда входят стробы чтения/записи обоих адресных пространств, а также ряд ответных сигналов, реализующих принцип квитирования.

- -SMEMR, -MEMR (Memory Read) -SMEMW, -MEMW (Memory Write) представляют собой стробы чтения/записи данных при обращении к памяти.

- -IOR (-I/O Read) ,-IOW (-I/O Write) то же при обращении к УВВ.

- -MEM CS16 (Memory Cycle Select) выбор цикла для памяти. Сигнал выставляется памятью для извещения задатчика о том, что она имеет 16-разрядную организацию.

- -I/O CS16 (-I/O Cycle Select) выбор цикла для УВВ. Ответный сигнал УВВ, извещающий задатчика о том, что оно является 16-разрядным.

- I/O CH RDY (I/O Channel Ready) готовность канала ввода-вывода. Сигнал снимается исполнителем, если он не успевает выполнить требуемую операцию в темпе задатчика и требуется удлинение цикла.

- -0WS (0 Wait States) 0 тактов ожидания. Формируется исполнителем при необходимости проведения цикла обмена без тактов ожидания. Единственный сигнал шины ISA, синхронизированный с тактами SYCLK.

- -REFRESH регенерация. Сигнал выставляется контроллером регенерации для информирования всех устройств на шине о выполнении цикла регенерации динамической памяти, что повторяется с периодом около 15 мкс.

#### Центральные сигналы управления

-MASTER — формируется устройством, желающим стать задатчиком на шине.

RESET DRV (Reset of Driver) — сброс устройства. Сигнал начальной установки всех устройств на шине.

- -I/O CHCK (I/O Channel Check) проверка канала ввода-вывода. Сигнал ошибки.

- СLК или SYSCLK (System Clock) системный такт. Меандр со скважностью 2. Во многих ЭМВ его частота равна 8 МГц независимо от тактовой частоты процессора.

- OSC не синхронизированный с SYSCLK сигнал кварцевого генератора с частотой 14,31818 МГц со скважностью 2.

#### Запросы на прерывание

IRQ0... IRQ 15 (Interrupt Request) — запрос прерывания. Не все из них выведены на слоты.

## Сигналы режима ПДП (DMA — Direct Memory Access)

DRQ0...DRQ7 (DMA Request) — запрос ПДП.

-DACK0...-DACK7 (DMA Acknolege) — подтверждение ПДП.

He все DRQ/DACK выведены на слоты.

T/C (Terminal Count) — окончание счета циклов передачи данных в режиме  $\Pi Д \Pi$ .

Сигнгал AEN, формируемый контроллером ПДП в этом режиме, обычно относят к группе адресных сигналов.

На шине кроме того имеются линии, по которым подается питание в устройства ЭВМ: GND - линия нулевого потенциала («земля»), +5B, -5B, +12B, -12B.

## 1.3.4. Временные диаграммы циклов шины ISA

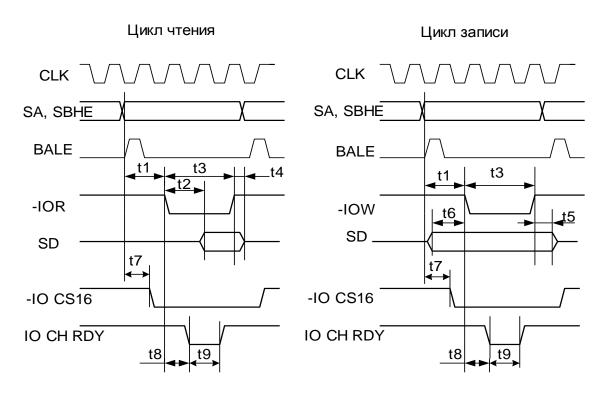

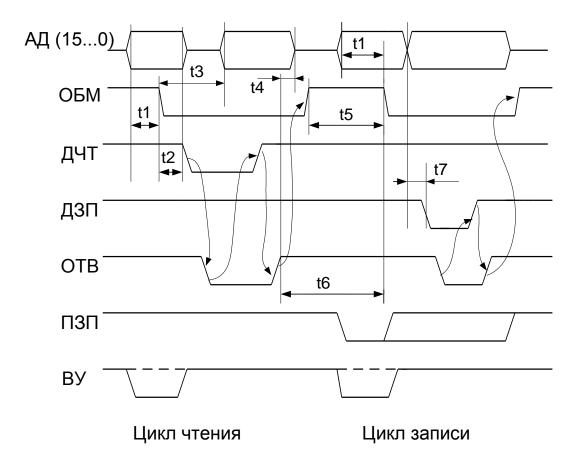

В рассматриваемой шине конкретный вид и параметры временных диаграмм зависят не только от типа цикла из указанных в п.1.3.2, но и от типа (память или УВВ), и разрядности ресурса доступа или передаваемой информации (8 или 16 бит), и от быстродействия ресурса, с которым ведется обмен. На рис. 1.3 приведены временные диаграммы выполнения циклов чтения и записи регистров ввода/вывода (портов). Об этом свидетельствуют командные сигналы –IOR и –IOW. По существу это диаграммы процессов, происходящих на шине при выполнении команд in и out процессором. Рис. 1.3 охватывает случаи обмена байтами (8 бит) и словами (16 бит), нормальный и удлиненный циклы обмена.

Если выполняется нормальный цикл доступа (ресурс не требует формирования тактов ожидания), то сигнал ІО СН RDY в течение всего цикла будет сохранять высокий уровень (H). В этом случае говорят, что сигнал «разрешен».

Если выполняется 8-разрядный обмен, то сигнал -IO CS16 в течение всего цикла имеет уровень Н («запрещен»). Если ресурс доступа (УВВ) формирует ответный сигнал -IO CS16, то выполняется 16-разрядный цикл обмена, который имеет другие временные параметры.

Таким образом, если сигналы IO CH RDY и -IO CS16 не участвуют в работе, то рис. 1.3 становится похожим на диаграммы синхронного обмена рис. 1.2, и временные параметры t1...t5 имеют тот же смысл. Отметим только некоторые моменты. На рис. 1.3 показана тактовая частота СLК. Этот сигнал фактически присутствует на шине, но сигналы шины с ним не синхронизированы (за исключением 0WS). На рисунке показан также сигнал ВАLE, который формируется задатчиком одновременно с установкой нового адреса на шине. Этот сигнал используется редко, но при наблюдении процесса обмена он удобен тем, что отмечает начало каждого цикла на шине.

В цикле записи на рис. 1.3 показано опережение на время t16 установки данных относительно строба записи. В [6] отмечается, что в некоторых компьютерах данные при записи устанавливаются после начала формирования строба. Важно то, что данные должны быть действительны на положительном спаде сигнала IOW (окончание интервала t3).

В табл. 1.1 приведены временные параметры диаграмм [7]. Следует обратить внимание, что в разных режимах работы шины один и тот же параметр принимает разные значения.

Если устройство, к которому выполняется обращение, является 16-разрядным, то оно должно не позже, чем через время t7 ответить установкой в низкий уровень (L) сигнала -IO CS 16. Тогда временные параметры цикла будут совсем другими (табл.1.1). При отсутствии ответного сигнала -IO CS 16 задатчик формирует временную диаграмму для 8-разрядного цикла обмена. Это пример реализации принципа квитирования.

Рис. 1.3. Временные диаграммы циклов доступа к ресурсу шины ISA

Если устройство-исполнитель не в состоянии поддерживать нормальный темп обмена, то для успешного завершения цикла оно должно не позже, чем через интервал t8 после установки командного сигнала «запретить», т.е. установить уровень L на соответствующей линии, ответный сигнал IO CH RDY. При этом задатчик формирует такты ожидания, и состояние линий шины сохраняется в течение всего промежутка времени, пока IO CH RDY запрещен. Длительность этого промежутка (t9) кратна

периоду тактовой частоты СLК и не должна превышать 15600 нс. В противном случае формируется запрос на немаскируемое прерывание процессора NMI. Такой цикл называется удлиненным.

Величина t9, указанная в табл. 1.1, является максимальной и определяется, по-видимому, допустимым значением периода регенерации. Более значительная приостановка работы шины влечет за собой потерю данных в микросхемах динамической памяти. В некоторых моделях ПЭВМ в качестве допустимых для длительности запрещенного IO CH RDY указываются более короткие промежутки времени. Удлиненный цикл под управлением ответного сигнала IO CH RDY является другим примером реализации принципа квитирования в шине расширения ISA.

Таблица 1.1 Некоторые временные параметры циклов обмена для шины ISA с тактовой частотой 8 МГц

| Обозна-  |                                | Для 8-р          | азрядного | Для 16-ра        | зрядного |

|----------|--------------------------------|------------------|-----------|------------------|----------|

| чение на | Содержательный смысл           | обмена время, нс |           | обмена время, нс |          |

| рис. 1.3 | параметра                      | задатчик         | ресурс    | задатчик         | ресурс   |

| t1       | Опережение установки адреса    | ≥102             | ≥91       | ≥102             | ≥91      |

|          | относительно команды           |                  |           |                  |          |

| t2       | Время установления данных      | ≤ 489            | ≤ 467     | ≤ 132            | ≤ 110    |

|          | после сигнала чтения           |                  |           |                  |          |

| t3       | Длительность команды           | ≥ 530            | ≥ 519     | ≥ 187            | ≥ 176    |

|          | чтения/записи                  |                  |           |                  |          |

| t4       | Перевод линий сигналов SD в    | ≤ 32             | ≤ 32      | ≤ 32             | ≤ 32     |

|          | третье состояние               |                  |           |                  |          |

| t5       | Удержание данных при записи    | ≥ 30             | ≥ 30      | ≥ 30             | ≥ 30     |

| t6       | Опережение установки данных    | ≥ 33             | ≥ 22      | ≥ 33             | ≥ 22     |

|          | относительно команды записи    |                  |           |                  |          |

| t7       | Задержка -IO CS 16 относитель- |                  |           | ≤ 126            | ≤ 90     |

|          | но установки адреса SA         |                  |           |                  |          |

| t8       | Задержка IO CH RDY             | ≤ 378            | ≤ 350     | ≤ 66             | ≤ 44     |

|          | относительно команды           |                  |           |                  |          |

| t9       | Длительность запрещенного      | до 15600 нс      |           |                  |          |

|          | состояния сигнала IO CH RDY    |                  |           |                  |          |

Временные диаграммы циклов обращения к памяти на шине выглядят качественно так же, как диаграммы, показанные на рис. 1.3, только в качестве командных сигналов используются стробы чтения/записи памяти (-MEMR,

-SMEMR, -MEMW, -SMEMW) и ответный сигнал -MEM CS 16. Значения временных параметров при обращении к памяти также будут другими. Следует напомнить, что обращение к памяти со стороны процессора производится по внутренней шине процессор-память. Платы расширения памяти через слоты ISA уже давно не подключаются. Обращение к памяти по шине ISA возможно со стороны ПУ в режимах прямого доступа к памяти (ПДП) или захвата шины. В этих случаях также возможен асинхронный обмен с управлением длительностью цикла ответным сигналом IO CH RDY, который может запрещаться платой памяти.

Режимы ПДП и захвата шины представляют собой способы высокоскоростного обмена информацией между периферийным устройством и основной памятью под управлением контроллера ПДП (собственно ПДП), или под управлением аналогичного контроллера в ПУ (в режиме захвата шины). При этом обмен происходит автономно от центрального процессора.

# 1.4. Внешние аппаратные прерывания

## 1.4.1. Особенности организации прерываний

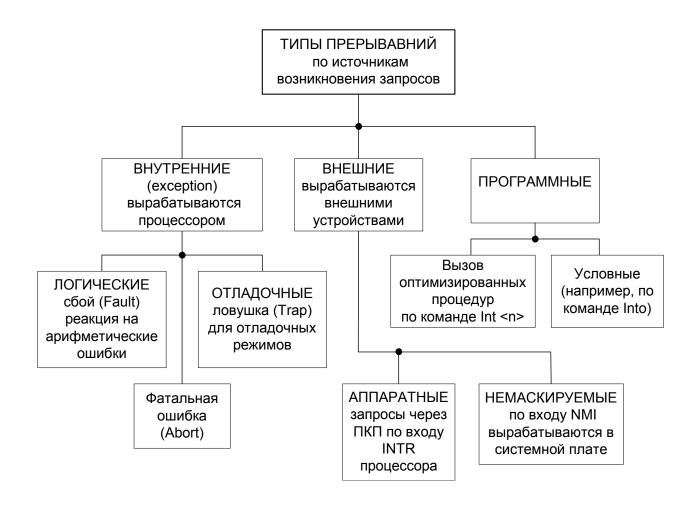

Под прерыванием понимается временное прекращение выполнения текущей программы и переключение процессора на выполнение другой программы под действием запроса на это прерывание и с последующим возвратом к исполнению прерванной программы. Во многих литературных источниках принята следующая классификация причин возникновения запросов на прерывания:

- предопределенные события в процессах, например, по команде в программе вызываются программные прерывания (в списках команд многих процессоров имеются соответствующие команды). Такие прерывания используются для обращения к часто применяемым процедурам, которые отлажены и поставляются производителями ЭВМ,

- непредопределенные события в процессах, возникающие в результате вычислений, например, переполнение или другие недопустимые ситуации,

- события, возникающие в периферийных устройствах, внешние прерывания.

Иногда в этот перечень причин включают прерывания в результате действий оператора и прерывания от таймера, но мы такие прерывания будем относить к внешним. Здесь нас, в первую очередь, будет интересовать этот третий тип прерываний.

В ІВМ РС-совместимых ПЭВМ внешние прерывания, которые называются также аппаратными, делятся на маскируемые и немаскируемые.

Запросы на немаскируемые прерывания вырабатываются системной платой при возникновении ошибки четности при обращении к памяти (сигнал –I/O CHCK шины ISA), при зависании в канале (длительное отсутствие разрешения сигнала I/O CH RDY) и в ряде других случаев [5]. В ПЭВМ, использующих другие шины, например PCI, также предусмотрены возможности вызова прерываний этого типа.

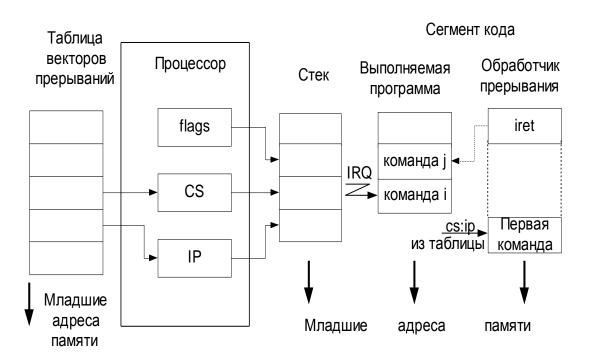

Все виды прерываний объединяет общий порядок перехода к обработке запроса на прерывание, который сводится к следующим действиям:

- завершение работы, которую нельзя прервать без потерь данных,

- сохранение состояния процесса, т.е. информации, необходимой для возврата к выполнению прерванной программы,

- определение начального адреса программы-обработчика для поступившего запроса,

- выполнение программы обработки прерывания, в конце которой обычно записана команда возврата из прерывания (для процессоров ряда i80x86 ... Pentium это команда iret),

- возврат в прерванную программу, т.е. выполнение команды iret.

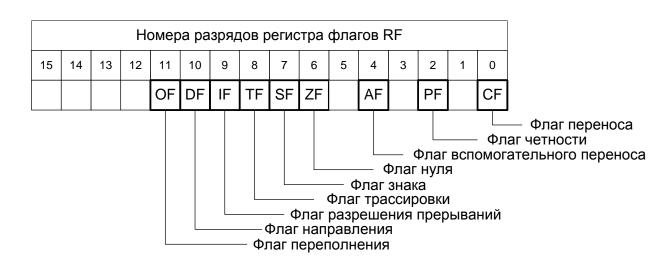

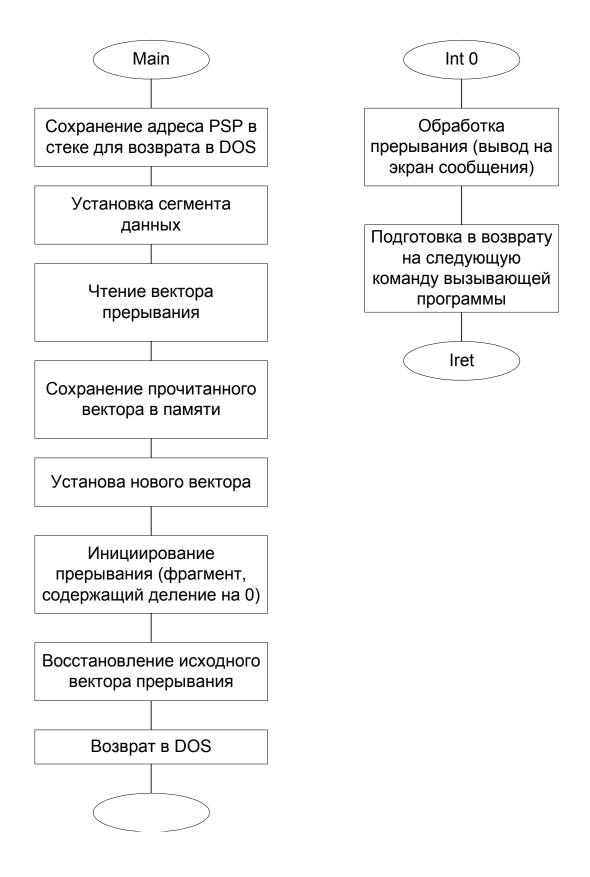

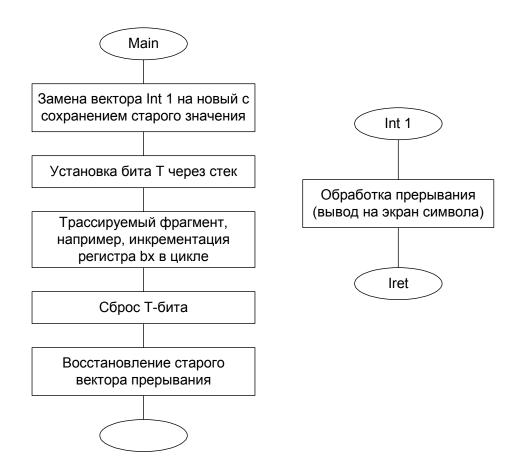

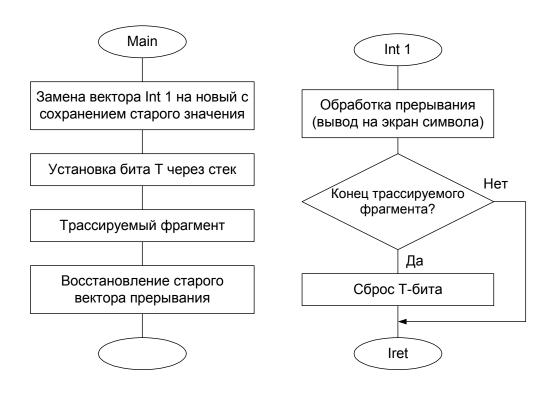

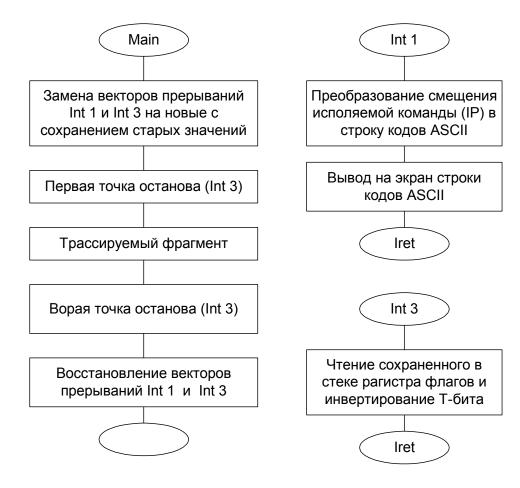

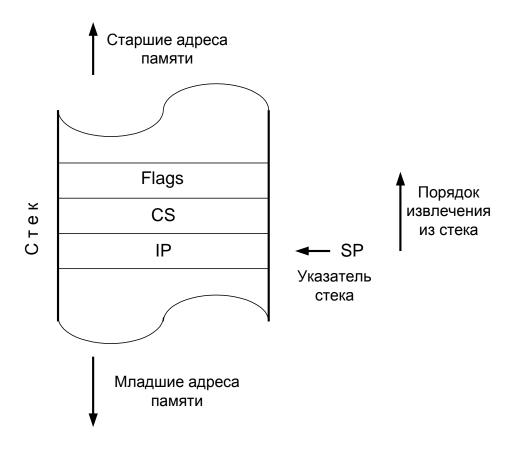

Рис. 1.4 иллюстрирует эту последовательность действий процессора. Напомним, что регистр флагов (flags) содержит информацию о состоянии процессора и программы, в сегментном регистре кода (CS) хранится адрес сегмента с машинными командами, к которому имеет доступ процессор, а указатель команд (IP) хранит смещение относительно начала командного сегмента следующей подлежащей выполнению команды. Адрес команды определяется как CS: IP.

Состояние процесса сохраняется В стеке. Необходимая продолжения работы исполняемой программы информация — это, прежде всего, адрес (точка) возврата и слово состояния программы. Пусть запрос IRQ поступил в момент выполнения і-й команды, а следующей должна была выполняться ј-я команда (см. рис. 1.4). В СЅ:ІР уже находится адрес ј-й команды. Процессор выполнит до конца і-ю команду, при этом, возможно, изменится состояние регистра флагов. И если внешние прерывания не перед входом в прерывание содержимое регистров замаскированы, процессора, показанных на рис. 1.4 (для процессоров і80х86), будет переписано в стек. Если для продолжения правильной работы прерванной программы требуется сохранение содержимого других регистров, то это нужно предусмотреть в обработчике.

**Определение начального адреса обработчика** выполняется поразному в ЭВМ различных архитектур. Известно два способа решения этой задачи: организация прерываний по радиальному и векторному принципам.

При радиальной организации адрес обработчика для каждого источника прерывания фиксирован аппаратно. Способ применяется в

системах с небольшим числом источников. Например, единственный внешний источник для микроконтроллера i8048 при прерывании вызывает переход по адресу 007. А в микропроцессоре K1801BM1 имеется три входа для запросов на радиальные прерывания.

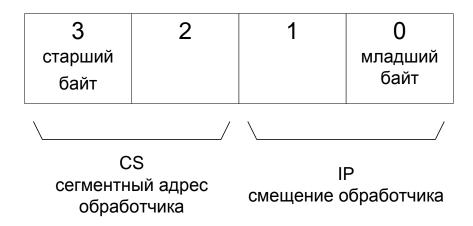

Рис. 1.4. Последовательность действий процессора при обработке запроса на прерывание: flags — регистр флагов; CS — сегментный регистр кода; IP — указатель команды

векторной организации адрес обработчика омкцп закодированном виде поступает в процессор из специального контроллера. Это происходит после прихода на вход векторного прерывания процессора сигнала запроса в результате выполнения процессором цикла чтения адреса вектора прерывания (АВП) или кода прерывания из контроллера прерывания. В ЭВМ на микропроцессорах i80x86...Pentium адреса обработчиков хранятся в таблице, которая находится в фиксированном месте памяти. Эта таблица называется таблицей векторов или дескрипторов прерывания (IDT — Interrupt Descriptor Table). Каждому источнику назначен свой номер в таблице. Векторная организация применяется в системах с большим числом источников прерываний. Этот способ рассматривается в дальнейшем применительно к системам на базе микропроцессора і80х86.

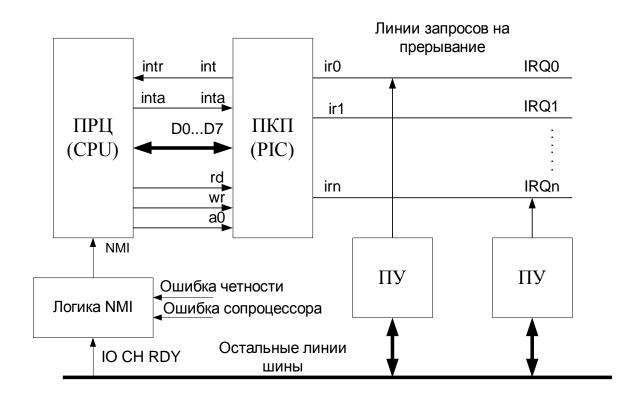

На рис. 1.5 приведена упрощенная структурная схема подключения периферийных устройств, способных вызывать прерывания, к центральной части ЭВМ. С помощью этой схемы можно проследить взаимодействие центрального процессора ПРЦ (CPU — central processing unit) с другими функциональными узлами при входе в прерывание. Подобная схема

применяется в ЭВМ различных архитектур. На рис. 1.5 использованы наименования входов/выходов, принятые для соответствующих блоков IBM PC-совместимых ПЭВМ.

На схеме показаны периферийные устройства, подключенные к линиям запроса на прерывания IRQ (interrupt request) системной шины (ISA). Эти линии подключены ко входам IR программируемого контроллера прерываний ПКП (PIC — programmable interrupt controller). Контролер назван программируемым, так как обычно возможна какая-то программная его настройка.

Рис. 1.5. Подключение периферийных устройств к системе обработки прерываний

Периферийное устройство выдает запрос на прерывание, т.е. устанавливает сигнал на шине IRQ и на соответствующем входе IR ПКП. Это приводит к активизации выхода INT контроллера прерываний и поступлению сигнала запроса на вход INTR процессора, который является входом сигнала запроса на векторное прерывание. Если флаг і разрешения внешних прерываний установлен (в регистре flags), процессор опрашивает вход INTR после завершения выполнения очередной инструкции.

Обнаружив сигнал на входе INTR, ПРЦ посылает подтверждение через выход INTA (Interrupt acknowledge). Приняв сигнал со входа INTA, ПКП

выставляет на шину данных D0...D7 номер или код прерывания, который считывается процессором.

Теперь процессор, получив необходимую информацию, завершает вход в прерывание:

- записывает в стек полный адрес следующей инструкции, содержащийся в регистрах **CS** и **IP**, а также текущее значение регистра флагов (см. рис. 1.4),

- обнуляет флаг і разрешения прерываний от внешних источников,

- считывает запись из таблицы векторов по номеру, полученному от источника прерывания, т.е. из ПКП (см. рис. 1.4, 1.5),

- выполняет переход по адресу, считанному из таблицы векторов прерываний (см. рис 1.4).

На этом вход в прерывание заканчивается. Результат — переход по адресу из таблицы векторов. По этому адресу должна находиться программа, которая выполняет обслуживание прерывания, т.е. производит необходимые манипуляции с регистрами периферийного устройства в соответствии с причиной прерывания.

Затем должен произойти возврат в прерванную программу — обратный переход по адресу, который был сохранен в стеке, а также должны быть восстановлены флаги процессора. Эти действия выполняются инструкцией iret, которая считывает из стека три слова и записывает их значения в регистры CS, IP и регистр флагов (см. рис 1.4).

#### Замечания:

- Для разрешения и запрета внешних прерываний в процессорах i80x86...Рentium предусмотрены команды установки и сброса флага i команды sti и cli. Процессоры других типов имеют аналогичные команды.

- При переходе процессора к обработке прерываний флаг і автоматически сбрасывается, чем запрещаются прерывания от любых внешних источников. Если для решения задачи требуется разрешить обработку более приоритетных запросов, то это должен сделать программист.

- В обычных ПЭВМ (архитектурная линия IBM PC) микросхема ПКП расположена внутри системной (материнской) платы. Шина, по которой осуществляется обмен данными между ПРЦ и ПКП (D0...D7 на рис. 1.5) находится на системной плате. А к слотам, через которые подключены ПУ, подведены только линии запросов IRQ. Так что можно сказать, что для самих ПУ прерывания носят радиальный характер в том смысле, что каждое ПУ подключено к своей индивидуальной линии IRQ, и для входа в прерывание ПУ только выставляет запрос и ничего более. А все существенные действия выполняет ПКП, расположенный в непосредственной близости от ПРЦ. Такая организация внешних прерываний налагает существенные ограничения при

попытке подключить дополнительные ПУ, которые должны бы вызывать прерывания, так как свободных линий IRQ может оказаться недостаточно, а подключение нескольких ПУ к одной линии вызывает трудности.

В других архитектурах, например, использующих шины Q-bus или VME-bus, к одной линии запроса на прерывание могут быть подключены несколько источников (по схеме монтажного ИЛИ). В этом случае контроллер каждого такого ПУ должен выполнять некоторые функции ПКП, в частности, при получении сигнала подтверждения ПУ должно выдать на шину данных (через слоты системной шины) код, идентифицирующий источник запроса, чтобы центральная часть ЭВМ могла правильно выбрать программу-обработчик. Например, по шине Q-bus передается адрес вектора прерываний, который используется непосредственно для обращения к таблице векторов. При этом вектор прерывания содержит не только адрес обработчика, но и слово состояния процессора, которое помещается в соответствующий регистр (аналог регистра flags).

- На рис. 1.5 показана цепь сигнала NMI, который формируется одним из чипсетов при поступлении на его входы сигнала, требующего немедленной реакции. Для многих ПЭВМ ранних моделей событиями, вызывавшими появление этих сигналов, являлись следующие ситуации:

- ошибка канала ввода/вывода (I/O CH RDY),

- ошибка сопроцессора,

- ошибка четности при обращении к памяти или к другому устройству, которое может сформировать сигнал -I/O CHCK.

В моделях последних лет единственным источником немаскируемого прерывания является ошибка четности (сопроцессоры в современных ПЭВМ не используются, а превышение длительности сигнала I/O CH RDY значения 15600 нс, указанного в табл. 1.1, немаскируемого прерывания не вызывает).

#### 1.4.2. Контроллер прерываний ПЭВМ

Как показано на рис 1.5, контроллер прерываний (ПКП) обеспечивает развязку между внешними источниками запросов на прерывание и процессором. Роль и место ПКП в системе прерываний в целом описана в п. 1.4.1. Однако практическое программирование процедур обработки прерываний требует более детального знакомства с этим функциональным узлом. Контроллеры прерываний в ЭВМ разных архитектурных линий имеют определенное сходство. В настоящем пособии ознакомимся с ПКП персональных ЭВМ. Такие контроллеры уже более двадцати лет выпускаются в виде больших интегральных схем. В современных ПЭВМ ПКП размещены в чипсетах обрамления центрального процессора.

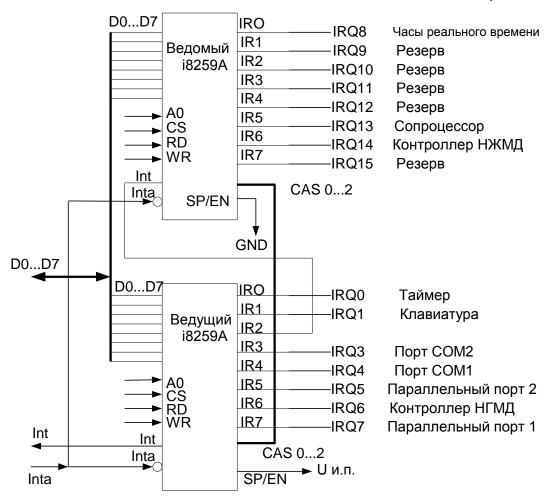

Прототипом современных ПКП является микросхема i8259A, которая имеет восемь входов запросов ir0...ir7 и использовалась в ПЭВМ класса IВМ РС/ХТ с шиной ХТ-Виѕ, называемой также восьмиразрядной шиной ISA. ПКП i8259A имеет сложную внутреннюю структуру, может программно настраиваться на различные режимы работы, допускает каскадное включение нескольких ПКП с целью увеличения количества линий запросов IRQ. Эти свойства обеспечивают гибкость и эффективность системы прерываний. Среди микросхем отечественных серий К580 и К1810 имеются аналогичные ПКП.

В первых 16-разрядных ПЭВМ использовались две микросхемы ПКП, включенные каскадно, как показано на рис. 1.6. Это позволило довести до 15 число линий IRQ на шине. Можно заметить, что к ведущему контроллеру можно подключить до восьми ведомых, тогда число линий запросов увеличится до 64. Каждый ПКП кроме входов/выходов ir0...ir7, D0...D7, Int, Inta, назначение которых объяснено в п. 1.4.1, имеет следующие управляющие входы:

- RD, WR входы сигналов чтения и записи. В контроллер записывается управляющая информация, из контроллера читается код, по которому будет определен вектор прерывания, а также информация о состоянии ПКП,

- CS выбор микросхемы,

- А0 вход нулевого разряда адреса, который используется при обращении к внутренним регистрам контроллера,

- SP/EN признак подчиненности (низкий уровень напряжения на этом входе переводит контроллер в состояние ведомого).

Кроме этого контроллеры связаны линиями CAS [2...0], по которым должен передаваться номер подчиненного ПКП. В более поздних моделях ПЭВМ структура, показанная на рис. 1.6, реализована в СБИС с полным сохранением логики работы пары микросхем ПКП i8259A.

Функции контроллера:

- фиксация запросов от внешних источников (на рис. 1.6. указано обычное для ПЭВМ распределение линий IRQ),

- формирование запроса Int на вход Intr процессора (рис. 1.5, 1.6),

- формирование кода прерывания и выдачу его по шине D0...D7 после прихода сигнала Inta и под действием сигнала RD (рис. 1.6),

- маскирование запросов, приходящих на входы ir0...ir7,

Рис. 1.6. Каскадное включение двух микросхем і8259А

• управление очередностью обработки запросов на прерывание в соответствии с назначенными приоритетами, т.е. выполнение функций арбитража.

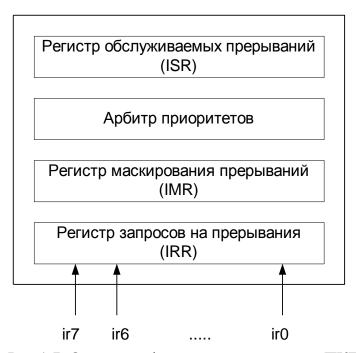

Для реализации этих функций контроллер содержит функциональные узлы, часть из которых показана на рис. 1.7:

- регистр запросов на прерывания (IRR Interrupt Request Register) для фиксации поступающих запросов,

- регистр маскирования прерываний (IMR Interrupt Mask Register) позволяет запретить действие одного или нескольких запросов,

- арбитр приоритетов (PR Priority Resolver) схема, выявляющая приоритеты запросов и выбирающая запрос с наивысшим приоритетом,

• регистр обслуживаемых прерываний (ISR — Interrupt Service Register) для хранения уровней запросов на прерывание, которые обрабатываются в данный момент.

Перечисленные регистры (IRR, IMR, ISR) являются восьмиразрядными по числу входов запросов микросхемы.

Для обращения к регистрам ПКП в адресном пространстве ввода/вывода ПЭВМ выделено две пары соседних адресов (портов). Для ведущего ПКП это адреса 020h и 021h, а для ведомого — адреса 0A0h и 0A1h.

ПКП может находиться в двух состояниях или режимах работы — инициализация и обслуживание запросов.

Инициализация. В этом состоянии ПКП находится после сброса. При этом он воспринимает команды инициализации, которые обозначаются ICW1...ICW4 (Initialization Command Words). Каждое из ICW имеет разрядность 8 бит и записывается в ПКП байтовыми командами вывода (out) по указанным адресам. ICW1 записывается по адресу 020h (0A0h), а ICW2...ICW4 — по адресу 021h (0A1h). Последовательность ICW устанавливает конфигурацию системы прерываний и некоторые особенности работы ПКП.

Рис.1.7. Основные функциональные узлы ПКП і8259А

В частности, выполняются следующие настройки:

- чувствительность ПКП к характеру сигналов по входам ir0...ir7 возможна настройка на работу по фронту или по уровню сигнала запроса,

- работа с единственным (для PC/XT) или с двумя ПКП (согласно рис.1.6, для PC/AT и более новых моделей),

- положение в каскаде (ведущий или ведомый),

- начальный номер (код) прерывания из набора последовательных кодов, генерируемых данным контроллером (команда ICW2). В стандартной конфигурации ПЭВМ в реальном режиме работы для ведущего контроллера устанавливается начальный код 08h, а для ведомого 70h.

При инициализации выполняется также ряд других настроек [3,6].

После выполнения инициализации ПКП переходит в **режим обслуживания прерываний или операционный режим.** В этом режиме ПКП воспринимает команды управления ОСW1...ОСW3 (Operation Control Words). Эти команды также являются 8-разрядными и посылаются в ПКП байтовыми командами вывода.

OCW1 — это байт маски запросов, посылается в IMR командой записи по адресу 021h (для ведомого 0a1h). Единица в разряде OCW1 означает запрет реакции ПКП на сигнал по соответствующему входу ir.

OCW2 — это команда управления приоритетами и способом завершения обслуживания прерывания, посылается по адресу 020h (0a0h).

OCW3 — это команда управления контроллером, посылается также по адресу 020h (0a0h).

Командами OCW2, OCW3 можно перевести ПКП в различные режимы обслуживания запросов и завершения обслуживания.

Предусмотрены следующие режимы обслуживания запросов:

- режим вложенных прерываний. Входам ir0...ir7 присвоены фиксированные приоритеты, которые убывают с ростом номера входа. Ir0 имеет высший приоритет,

- режим циклической обработки запросов. После обработки прерывания соответствующему запросу присваивается низший приоритет, остальные приоритеты циклически сдвигаются,

- режим адресуемых приоритетов. Командой можно присваивать запросу высший приоритет, приоритеты остальных запросов циклически сдвигаются,

- режим опроса. В этом режиме ПКП не формирует сигнала Int. Процессор «узнает» о наличии запросов путем чтения IRR,

- режим специальной маски. Позволяет отменить приоритетное упорядочение обработки запросов и обрабатывать их по мере поступления (в ПЭВМ не применяется).

Командами OCW2, OCW3 можно также установить автоматическое или неавтоматическое завершение прерывания. При автоматическом завершении соответствующая заявка в ISR сбрасывается при поступлении в ПКП сигнала Inta. Использование этого режима завершения влечет ряд трудностей при программировании [8].

Неавтоматическое завершение прерывания требует, чтобы в программе обработки были выполнены команды сброса соответствующего бита в регистре ISR. Возможно специфицированное и обычное завершение

прерывания. В первом случае выполняется команда сброса конкретного бита в регистре ISR. При обычном завершении выполняется сброс бита с максимальным приоритетом в ISR. В обоих случаях требуется посылка ОСW2. Так как обрабатываемое прерывание является наиболее приоритетным, то достаточно обычного завершения, которое выполняется путем записи кода 020h по адресу 020h (0a0h). Этот простой способ сброса заявки в ISR и рекомендуется для использования при программировании процедур обработки прерывания.

Командой ОСW2 можно выбрать один из режимов управления приоритетами. В ПЭВМ ряда IBM PC/XT/AT в результате работы программ начальной инициализации после включения питания ПКП устанавливается в режим вложенных прерываний с фиксированными приоритетами. В отдельном ПКП приоритеты заявок возрастают от ir7 к ir0. Из рис. 1.6 видно, что высшим приоритетом обладает запрос по шине IRQ0, а низшим — запрос IRQ7. Приоритеты запросов, поступающих на ведомый ПКП, находятся между приоритетами IRQ1 и IRQ3.

**Замечание.** Еще раз отметим, что переход к обработке внешнего прерывания производится процессором при сброшенном флаге і, поэтому разрешение обработки заявок с более высокими приоритетами возлагается на программиста.

Относительно исходного (после начальной инициализации) режима завершения прерываний имеются противоречивые сведения. В большинстве источников, например [8], указывается, что стандартным является режим неавтоматического завершения, т.е. сброс ISR возлагается на программиста. В практике составителей настоящего пособия также не встречался иной вариант.

При наличии нескольких заявок от разных источников выполняется та заявка, у которой приоритет выше. Заявки от отдельных входов IR можно замаскировать. Функции маскирования и выбора наиболее приоритетной заявки обеспечиваются тремя байтовыми регистрами ПКП и арбитром приоритетов (см. рис. 1.7).

Каждый из входов IRх в контроллере подключен к разряду x регистра IRR через входной вентиль. Вентиль открыт, если в регистре маски IMR сброшен разряд x. Регистр маски подключен к порту по адресу 021h (0a1h). Таким образом, для разрешения запросов по входу IRx нужно, чтобы разряд x порта 021h (0a1h) был сброшен.

Рассмотрим возможное прохождение сигнала прерывания от некоторого внешнего источника, подключенного к контроллеру прерываний с помощью линий IRQ.

Пусть поступление запросов по линии IRQx и по соответствующему входу IRx ПКП разрешено. Если в регистре запросов IRR разряд x сброшен, то по фронту сигнала IRQx в разряд x регистра IRR запишется единица.

Запрос запоминается, и арбитр приоритетов по значению регистра ISR принимает решение о возможности обслуживания запроса.

Заявка x из регистра IRR может быть принята к обслуживанию, если в регистре ISR не зафиксированы заявки от входов с номером  $y \le x$ . Контроллер выставляет сигнал INT. Заявка принимается к обслуживанию, когда будет получен ответный сигнал INTA. Контроллер обнуляет бит x в IRR и устанавливает бит x в ISR, затем выставляет на шину данных номер прерывания, соответствующий этой заявке.

После того, как заявка x принята к обслуживанию, установленный в ISR бит x блокирует обслуживание заявок с номерами  $y \ge x$ . Это означает, в частности, что блокированы следующие заявки от входа x. Для снятия маскирования необходимо, чтобы программа обслуживания прерывания в конце работы сбросила бит x в ISR. Сброс выполняется записью в порт 020h байта со значением 03xh (команда специфицированного завершения прерывания, OCW2), где x = 0...7 — номер входа IR контроллера прерываний. Альтернативный вариант сброса — запись в порт 020h (0a0h) байта со значением 020h (команда обычного завершения прерывания, OCW2). В результате в ISR сбрасывается заявка с наименьшим номером: это именно та заявка, которая обслуживается в текущий момент как наиболее приоритетная.

**Замечание.** Все пояснения, сделанные на сс. 29...31 относительно управления контроллером прерываний в режиме обслуживания, в равной мере относятся как к ведущему ПКП, так и к ведомому. Т.е. для маскирования прерываний от запросов, поступающих на входы ведомого ПКП (IRQ8...IRQ15), нужно устанавливать соответствующие разряды в IMR ведомого ПКП по адресу 0a1h.

Для обычного сброса заявки в ISR, если запрос поступил в ведомый ПКП, нужно записать код 020h как по адресу 0a0h (для сброса ISR ведомого ПКП), так и по адресу 020h (для сброса ISR ведущего ПКП). Это необходимо потому, что запросы IRQ8...IRQ15 после обработки в ведомом ПКП транслируются на вход IR2 ведущего контроллера. Таким образом для сброса заявки в ведомом ПКП нужно в обработчике прерывания записать следующую последовательность команд:

mov al, 020 out 020,al out 0a0, al,

а для сброса заявки в ведущем ПКП — только две первые их них.

## 1.5. Проектирование плат расширения

В современной вычислительной технике преобладают устройства с так называемой магистрально-модульной организацией, когда основные

функциональные узлы ЭВМ стандартным образом подключены к магистрали или шине, называемой системной. Здесь речь идет об устройствах и системах, единого Совокупность конструктивно исполненных В виде блока. ограничений, обеспечивающих логическую, электрическую (или вообще физическую), конструктивную совместимость составляет существо понятия межмодульного интерфейса. В сложных современных вычислительных системах, в том числе в ПЭВМ, наблюдается иерархическая организация шин, используются различные интерфейсы, и понятие системной оказывается размытым, но на одном «этаже» такой системы шин сохраняются все свойства классической магистрально-модульной структуры.

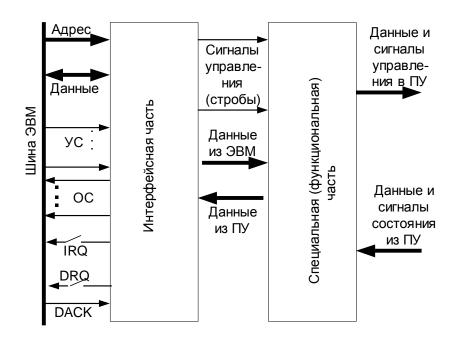

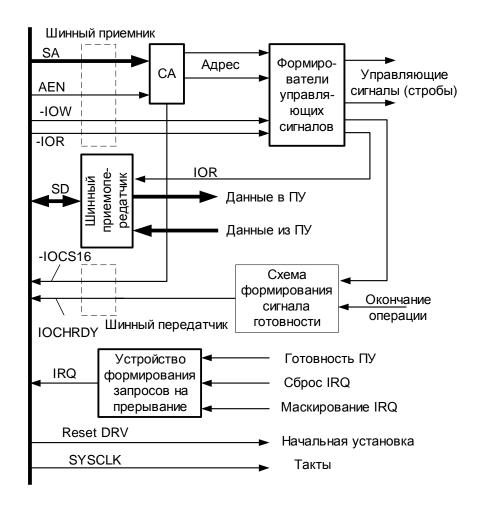

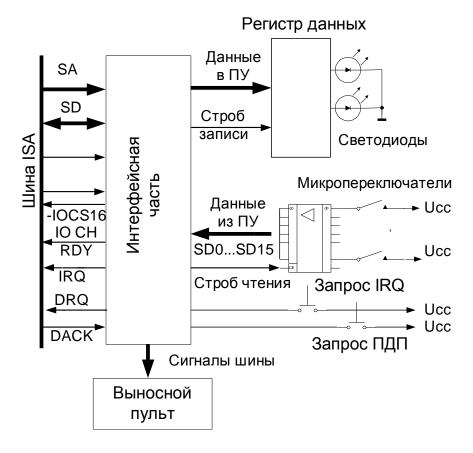

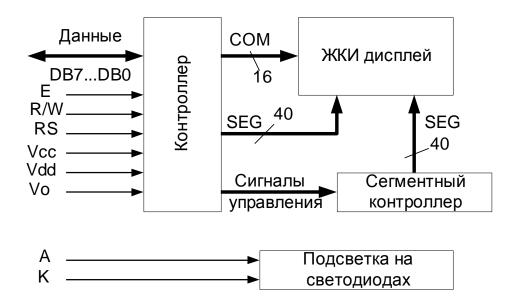

В практике создания управляющих вычислительных комплексов (УВК) с широким использованием стандартных вычислительных средств часто возникает необходимость разработки нестандартных периферийных плат, позволяющих добиться желательных свойств комплекса. В частности, это могут быть платы сопряжения УВК с объектом управления. Такую специализированную плату можно представить состоящей из двух частей, как это показано на рис. 1.8:

- интерфейсная часть, обеспечивающая сопряжение с шиной данного стандарта,

- специальная или функциональная часть, обеспечивающая информационный обмен с собственно периферийным устройством (ПУ).

Эти устройства называются контроллерами ПУ. В качестве примера можно привести контроллеры стандартных ПУ (накопителей на магнитных дисках, лентах) или в управляющих ЭВМ контроллеры электроприводов, электроавтоматики и т.п. На рис. 1.8 показано, что со стороны центральной части ЭВС контроллер подключен к шинам адреса и данных (в ряде интерфейсов они являются совмещенными), к линиям управляющих сигналов шины. На рис. 1.8 показаны УС — командные и управляющие а также ОС — ответные сигналы контроллера, шины, корректирующие темп обмена в соответствии с протоколом. Так как обмен информацией со многими ПУ может происходить в режиме прерывания или ПДП, то на схеме показано подключение контроллера к линиям запросов (IRQ, DRQ), а также к линии подтверждения прямого доступа (DACK). В некоторых стандартах требуется подтверждение и прерывания (на схеме не устранения конфликтов другими устройствами, показано). Для присутствующими на шине, подключение платы к линиям IRQ и DRQ часто делается через перемычки или микровыключатели. Использование режимов прерывания и ПДП для обмена с одним контроллером встречается редко, но примеры имеются (контроллеры накопителей на магнитных дисках).

Интерфейсная часть контроллера ПУ должна формировать сигналы управления элементами специальной части. Это, как правило, сигналы чтения и записи регистров (стробы). Ответные сигналы от специальной части, отражающие состояние объекта управления (ПУ), принимаются

интерфейсной частью по командам чтения по внутренней шине данных, поэтому специально на схеме не показаны.

В специализированных УВК получили распространение несколько межмодульных параллельных системных интерфейсов, например, Q-bus, ISA,

Рис. 1.8. Обобщенная структурная схема платы сопряжения (контроллера ПУ)

PCI и ряд других. Несмотря на значительные различия между этими шинами, организация обмена информацией по ним имеет общие принципы, сформулированные в п.1.2

Функциональная схема интерфейсной части контроллера ПУ определяется используемым интерфейсом и для данной шины является унифицированной. Если контроллер является ведомым устройством, то его интерфейсная часть должна распознать факт обращения именно к данному устройству, под управлением сигналов от ведущего устройства принять или выдать информацию на шину данных, сопроводив эти действия ответными сигналами в случае необходимости. Если контроллер является устройством ведущим, то он формирует сигналы на захват магистрали (режимы прямого доступа к памяти или захвата шины) и после получения доступа к ней формирует сигналы управления обменом.

Таким образом, для разработки интерфейсной части нестандартной платы ЭВМ необходимо изучить ограничения, налагаемые используемым интерфейсом. В документации на интерфейс описаны все электрические линии, управляющие сигналы, их функции в различных режимах работы шины, причинно-следственные отношения между сигналами, их временные и

электрические характеристики, конкретные типы соединителей (разъемов), конструктивные требования к платам и т.п.

В качестве примера рассмотрим обобщенную функциональную схему платы расширения для шины ISA. Типовая функциональная схема интерфейсной части такой платы приведена на рис. 1.9. Ограничимся случаем, когда такая плата не может быть задатчиком на шине. Временные диаграммы взаимодействия центрального процессора с контроллером ПУ приведены на рис. 1.3, временные параметры указаны в табл. 1.1.

В соответствии с принципом унификации (п. 1.2) при проектировании платы расширения необходимо обеспечить все виды совместимости. Конструктивная совместимость обеспечивается на этапе конструкторского проектирования путем соблюдения размеров и других требований, указанных в спецификации шины. Здесь уделим внимание только информационной и электрической совместимости.

Информационная совместимость обеспечивается выполнением требований протокола взаимодействия устройств на шине, правильным использованием линий интерфейса. Информационная и электрическая совместимость тесно связаны в части выполнения элементами схемы устройства требований к временным задержкам и последовательности срабатывания. Рассмотрим это подробнее на примере требований к интерфейсной части контроллера ПУ шины ISA (см. рис. 1.3 и 1.9).

Распознавание факта обращения именно к нашему контроллеру выявляет селектор адреса СА за время  $t_{CA}$ . В цикле чтения под действием выходного сигнала от СА и строба –IOR узел формирователей управляющих сигналов (ФУС) вырабатывает строб чтения выбранного регистра контроллера (которым, например, открываются ключи, подающие сигналы на линии «данные из ПУ»). Пусть ФУС вносит задержку  $t_{\alpha}$ , а схема чтения выбранного регистра вносит задержку  $t_{\beta}$ . ФУС также под действием строба чтения –IOR шины за то же время  $t_{\alpha}$  формирует внутренний сигнал, настраивающий шинный приемопередатчик на чтение ПУ (передача справа налево по рис. 1.9). Сам приемопередатчик вносит задержку  $t_{\gamma}$ . Тогда для правильной работы схемы необходимо  $t_1 > t_{CA}$ , а также  $t_2 > t_{\alpha} + t_{\beta} + t_{\gamma}$ . В этих рассуждениях не учитывалась возможная задержка, вносимая шинным приемником, который показан пунктиром на рис. 1.9.

Рис. 1.9. Функциональная схема интерфейсной части контроллера ПУ

В цикле записи на прохождение сигналов данных из шины через приемопередатчик (в этом цикле он настроен на передачу слева направо) времени вполне достаточно (рис.1.3). Но для правильного завершения цикла и сохранения данных в выбранном регистре требуется, чтобы данные не исчезли раньше, чем закончится строб, выработанный узлом ФУС. Т.е. необходимо, чтобы выполнялось  $t_{\alpha} < t_{\gamma} + t_{5}$ .

Здесь  $t_1$ ,  $t_2$  и  $t_5$  — требования стандарта шины, а  $t_{CA}$ ,  $t_{\alpha}$ ,  $t_{\beta}$  и  $t_{\gamma}$  — динамические параметры использованных элементов схемы.

Аналогичные соотношения легко получить и для элементов, формирующих сигналы -IOCS16 и IOCHRDY.

На рис. 1.9 показано устройство формирования запросов на прерывание. В него приходят три сигнала. «Готовность ПУ» — это сигнал, означающий, что наступило событие, требующее переключения программы на обработку прерывания. Т.е. этот сигнал инициирует установку IRQ. Желательно проектировать схему так, чтобы запрос IRQ сбрасывался по команде во время обработки прерывания. «Сброс IRQ» может быть инициирован командой записи так, чтобы один из разрядов записываемых

данных обеспечивал это действие. Многие контроллеры ПУ допускают маскирование прерываний по программе. Это также может быть сделано командой записи в соответствующий регистр управления данного ПУ. Эту возможность отражает на рис 1.9 сигнал «маскирование IRQ».

Для начальной установки контроллера ПУ, когда это необходимо, используется сигнал Reset DRV. Тактовые импульсы SYSCLK также могут быть использованы для работы контроллера, хотя нужно отметить, что в простейших случаях (чтение и запись) в них нет необходимости, так как стробов шины ISA достаточно для управления этими процессами.

Понятие электрической совместимости включает в себя также соблюдение ограничений по нагрузочной способности элементов. На шине ISA могут быть использованы устройства (элементы), имеющие выходы типа ТТЛ (транзисторно-транзисторная логика), выходы типа ОК (открытый коллектор) и элементы с тремя состояниями выхода. Элементы с выходами ТТЛ или ОК являются либо только входными, либо только выходными для устройства. Элементы с тремя состояниями выхода могут быть входными, выходными и, кроме этого, находиться в третьем состоянии.

Например, для сигналов, перечисленных в п. 1.3, установлено, что формирователи сигналов адресных (SA, LA, SBHE), данных (SD), стробов чтения/записи памяти/УВВ, а также тактовых импульсов SYSCLK должны быть с тремя состояниями выхода. Командные сигналы BALE, RESET DRV, запросы на прерывание (IRQ), сигналы режима ПДП (DRQ, DACK, T/C, AEN), а также OSC должны формироваться элементами с выходами ТТЛ. Ответные сигналы -МЕМ СS 16, -I/O CS 16, -I/O CH RDY, -I/O CH CK, -0WS, а также сигналы центрального управления — REFRESH и -MASTER должны формироваться элементами с ОК.

При проектировании платы расширения требуется обеспечить, чтобы элементы, формирующие выходные сигналы платы, были способны обеспечить выходные токи низкого уровня 24 мА (втекающий ток при низком уровне выходного сигнала). Нагрузочная способность при высоком уровне выходного сигнала должна быть не хуже, чем 3 мА.

Потребление по входам элементов, подключенных к шине ISA, не должно превышать 0,8 мА (по линии с ОК не более 0,4 мА для каждого слота) при низком уровне сигнала передающего элемента. Потребление по входам при высоком активном уровне сигнала не должно превышать 0,04 мА (для линии с ОК 0,02 мА).

Приведенные электроэнергетические ограничения установлены достаточно давно и ориентированы на применение устаревшей элементной базы. В настоящее время на шине вряд ли можно встретить устройства со столь значительным потреблением тока. Современные микросхемы чаще всего выполнены по КМОП технологии. Это значит, что потребление по их входам не превышает нескольких микроампер, что в тысячи раз меньше допустимых значений. В то же время нагрузочная способность выходов

современных КМОП элементов превышает 10 мА. В этих пределах гарантируется их совместимость с ТТЛ элементами по уровням сигнала и достаточно хорошие динамические параметры. Следовательно, в реальном проектировании, используя современные элементы, практически можно, по крайней мере, вдвое сократить требования к нагрузочной способности используемых элементов по выходам. Необходимость включать в состав платы показанные на рис. 1.9 пунктиром приемопередатчики и приемники при этом также отсутствует.

При проектировании плат расширения традиционно используются интерфейсные микросхемы, среди которых имеются БИС, ориентированные на применение в конкретных шинах. Однако появление микросхем гибкой логики со средствами автоматизации проектирования делает доступным и целесообразным использование именно их при реализации интерфейсной части контроллеров. При этом повышается надёжность и гибкость разрабатываемых устройств, снижается время, необходимое на их разработку и отладку.

Кроме ограничений по нагрузке в статике необходимо выполнить ряд требований к размещению элементов на плате (длина проводника от контакта внешнего разъема до вывода микросхемы не должна превышать 65 мм), к емкости нагрузки (не более 20 пФ на контакт разъема) и к фронтам выходных сигналов передатчиков (не хуже 3 нс), соблюдение которых гарантирует допустимый уровень помех [7].

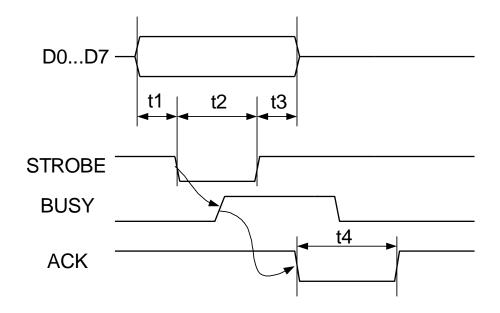

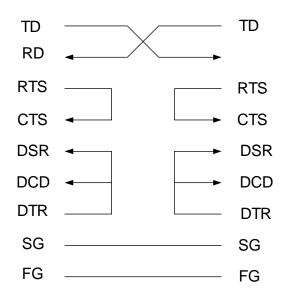

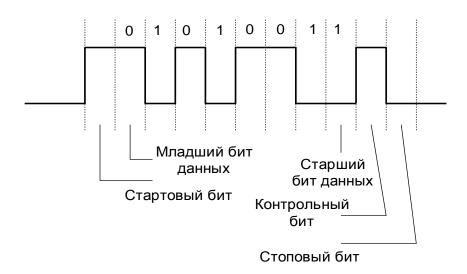

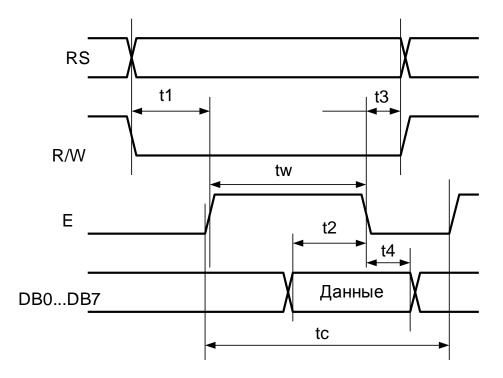

# 1.6. Параллельный порт и интерфейс Centronics

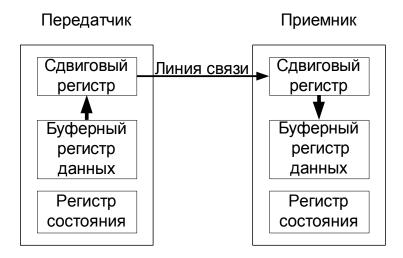

## 1.6.1. Основные положения. Разновидности параллельного порта

Параллельный порт был включен в состав ПЭВМ с 1981 г. для подключения принтеров, поэтому он называется LPT-портом (LPT – Line Printer, т.е. линейный принтер или принтер построчной печати, хотя к такому порту подключаются принтеры и других типов). Однако, благодаря удобству программирования и простоте подключения к нему, он широко применяется для сопряжения персональных ЭВМ с разнообразными периферийными устройствами (ПУ) и приборами. Отмечается, в частности, безопасность для ПЭВМ подключения к параллельному порту внешних устройств [6]. Удобство подключения обусловлено тем, что такой порт имеется у всех ПЭВМ, а соответствующий разъем установлен снаружи, и для подключения не нужно вскрывать корпус системного блока. Отсутствие шин питания на разъеме не вызывает существенных затруднений. В качестве недостатков интерфейса принято указывать невысокое быстродействие и ограничения на протяженность линий связи (до 2 м). Заметим, что скорость передачи данных через параллельный порт все же выше, чем через последовательный, а в