DOI: 10.18721/JCSTCS.14306 УДК 621.375

# **ZERO-DRIFT OPERATIONAL AMPLIFIERS**

A. Assim<sup>1,2</sup>, E.V. Balashov<sup>2</sup>

<sup>1</sup> Salahaddin University, Erbil, Iraq;

<sup>2</sup> Peter the Great St. Petersburg Polytechnic University, St. Petersburg, Russian Federation

This article considers the design and implementation of four different zero-drift operational amplifiers with 50 nm technology CMOS and compares their characteristics. The aim is minimizing input offset voltage and flicker noise. Offset voltage is unavoidable in operational amplifiers, because no two transistors can be identical. A small difference in their dimensions (length or width) gives rise to this undesirable effect, the value of offset voltage in common operational amplifiers is less than 10 mV. In this article, two major techniques of dynamic offset cancellation, chopping and auto-zeroing, are considered. The operational amplifier with chopping shows the best result among the four amplifiers.

**Keywords:** zero-drift operational amplifiers, auto-zeroing, chopper amplifier, offset voltage reduction, CMOS.

Citation: Assim A., Balashov E.V. Zero-drift operational amplifiers. Computing, Telecommunications and Control, 2021, Vol. 14, No. 3, Pp. 64–74. DOI: 10.18721/JCST-CS.14306

This is an open access article under the CC BY-NC 4.0 license (https://creativecommons.org/ licenses/by-nc/4.0/).

## ОПЕРАЦИОННЫЕ УСИЛИТЕЛИ С НУЛЕВЫМ ДРЕЙФОМ

А. Ассим<sup>1,2</sup>, Е.В. Балашов<sup>2</sup>

<sup>1</sup> Университет им. Салахаддина, Эрбиль, Ирак; <sup>2</sup> Санкт-Петербургский политехнический университет Петра Великого, Санкт-Петербург, Российская Федерация

Рассмотрена разработка и реализация четырех различных операционных усилителей с нулевым дрейфом с использованием технологии КМОП 50 нм. Целью является минимизация входного напряжения смещения и фликкерного шума. Напряжение смещения неизбежно в операционных усилителях, так как невозможно изготовить два транзистора одинаковых размеров. Небольшая разница в их размерах (длина или ширина) вызывает этот нежелательный эффект, значение напряжения смещения в обычных операционных усилителях меньше 10 мВ. В статье описаны два основных метода: коррекция дрейфа нуля на основе модуляции/демодуляции сигнала и периодическая коррекция дрейфа. Операционный усилитель с техникой коррекции дрейфа нуля на основе модуляции/демодуляции сигнала показал наилучшие результаты среди четырех усилителей.

**Ключевые слова:** операционные усилители с нулевым дрейфом, периодическая коррекция дрейфа, коррекция дрейфа нуля на основе модуляции и демодуляции сигнала, снижение напряжения смещения, КМОП.

Ссылка при цитировании: Assim A., Balashov E.V. Zero-drift operational amplifiers // Computing, Telecommunications and Control. 2021. Vol. 14. No. 3. Pp. 64–74. DOI: 10.18721/JC-STCS.14306

Статья открытого доступа, распространяемая по лицензии СС ВУ-NC 4.0 (https://creative-commons.org/licenses/by-nc/4.0/).

#### Introduction

Operational amplifiers are among the most versatile building blocks that are used in many modern analog and digital systems including filters, active rectifiers, current-to-voltage converters, etc. [3–18]. Due to their robust performance and righteous characteristics, they mimic an ideal amplifier, namely high input resistance, low output resistance, high gain, and stability [17]. Like in any other device, getting ideal characteristics in practice is impossible; therefore, tradeoffs must be made between the parameters (noise, linearity, gain, supply voltage, voltage swings, speed, input/output impedance and power dissipation) according to the required application [3]. Indeed, such tradeoffs pose many challenges to the designer, requiring solid knowledge and experience to reach an acceptable compromise.

Offset voltage is a dominant error source for operational amplifiers, especially at low frequencies. It has direct proportionality with flicker noise, hence in this article offset reduction is measured through reduction in flicker noise. Offset voltage exists due to mismatch in transistor sizes. Amplifiers without offset compensation have flicker noise as high as 400 nV/ $\sqrt{Hz}$  [1, 2]. There are three major techniques that are commonly used to reduce offset voltage and flicker noise: trimming, auto-zeroing, and chopping. Trimming is done during fabrication to eliminate offset. In order to correct the dimensions of the circuit elements, laser is used. It does not belong to the category of zero-drift operational amplifiers. Because of that, trimming is not considered in this article. Auto-zeroing's principle of operation is based on sampling. The offset voltage is captured in one clock phase (a capacitor is charged to such value, with an opposite polarity) and then subtracted in the next clock phase. Chopping is based on continuous-time modulation. The input signal is modulated by the first chopper to a higher frequency. The offset voltage is added to it, then this signal will be amplified, and the second chopper modulates the offset voltage and demodulates the modulated input signal, hence the offset is converted to a higher frequency. Since the offset voltage undergoes modulation in chopper amplifier, a ripple is observed at the amplifier's output. Both mentioned techniques are dynamic techniques that continuously reduce offset. They also reduce low frequency noise and offset drift as a function of temperature or time, in this paper, auto-zeroing and chopping methods are implemented practically with different architectures. These include a fundamental auto-zeroing amplifier, continuous-time auto-zeroing, chopper amplifier and a combination of chopping and auto-zeroing together.

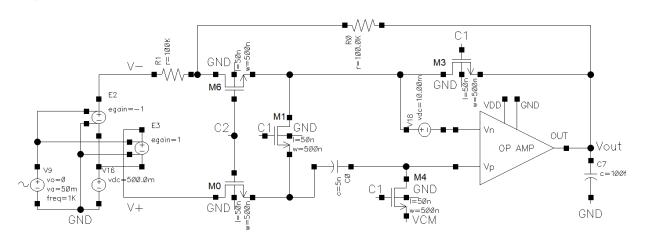

#### Fundamental auto-zeroing amplifier

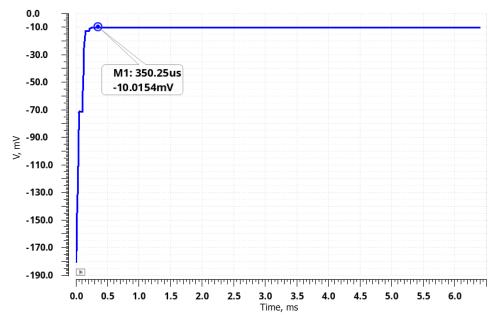

A principal auto-zeroing amplifier is provided in Fig. 1. It consists of an operational amplifier with 5 transistors that act as switches, the differential input signals are given on the input. Clock signals (C1 and C2) are out of phase by 180 degrees. The transistors (M1, M3 and M4) are controlled by clock signal C1, while M0 and M6 transistors are controlled by clock signal C2. The output signal is single-ended, labeled as (Vout). The proposed amplifier operates in the following manner. On the first cycle when the input clock C1 is on (C2 is off), both of the differential inputs (labeled as V– and V+) are shorted. The feedback loop (R0 resistor and transistor M3) is closed and the offset that appears at the output is fed back into the input. Thus, the capacitor (C0 – 5 nF) is charged to the offset voltage value (-10 mV), as shown in Fig. 2. On the other cycle when C2 is on (C1 is off), the amplifier works as usual, meaning that the differential inputs appear at the amplifier's input (they are not shorted). At the same time the capacitor charge compensates the offset voltage, because they are opposite in sign. This will result in zero offset voltage at the input. The capacitor takes around 350.2 µs to charge and begins to compensate the offset voltage.

The fundamental auto-zeroing amplifier isn't suitable for continuous-time applications, therefore, another architecture is introduced below, namely "Continuous-time auto-zeroing".

Computing, Telecommunications and Control

Fig. 1. Amplifier with auto-zeroing

Fig. 2. Voltage on capacitor C0 versus time

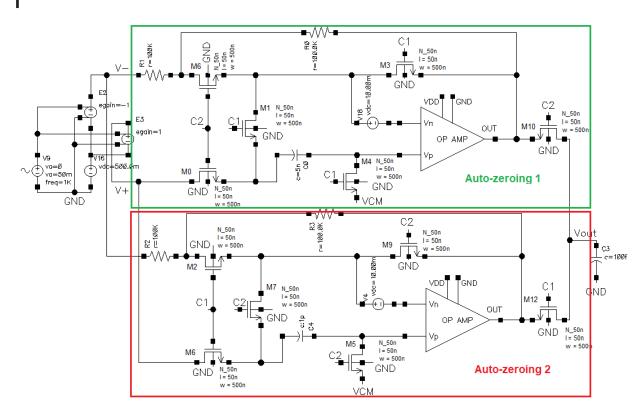

#### Continuous-time auto-zeroing

The fundamental auto-zeroing amplifier was meant to be used in non-continuous applications. Except certain applications, it should not be used, when continuous-time signals are needed, as in voice amplifiers or analog-to-digital converters. A configuration exists that is known as continuous-time auto-zeroing amplifier (CTAZ or ping-pong amplifier). It is a general term that can be used for any amplifier that implements two identical sub-amplifiers with opposite clock pulses to achieve a continuous signal at the output. A realization of such amplifier is given in Fig. 3. It consists of two identical operational amplifiers, 2 feedback resistors (100 k $\Omega$ ), 5 transistors that are controlled by two out of phase clock signals C1 and C2; the output is a single-ended signal taken from Vout pin. Its working principle can be summarized in two stages. The first stage, when C2 is high (C1 is low), the upper amplifier receives the signal from the differential inputs, amplifies it and feeds it to the output (Vout). The lower amplifier's inputs are shorted and it's in compensation mode. In the next stage, when C2 turns into low (C1 is high), the lower amplifier amplifier

Fig. 3. Continuous-time auto-zeroing amplifier

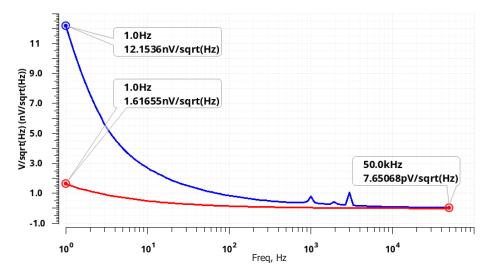

Fig. 4. PSS noise results for circuit in Fig. 3 before and after compensation (blue and red)

the signal, and the output voltage is taken from the lower amplifier. The upper amplifier compensates for offset, this results in a continuous signal at all times at the output. Fig. 4 shows flicker noise reduction.

Besides auto-zeroing, another popular offset reduction technique known as "chopping" exists. It has better flicker-noise reduction characteristics as demonstrated below.

### Chopping

Chopping is a major offset-reduction technique. It is widely used to reduce offset voltage [4, 8-11, 20-24]. It is favorable in applications where a continuous-time signal is needed. Unlike auto-zeroing

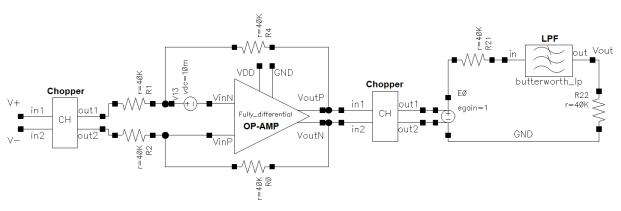

Fig. 5. Chopper amplifier circuit

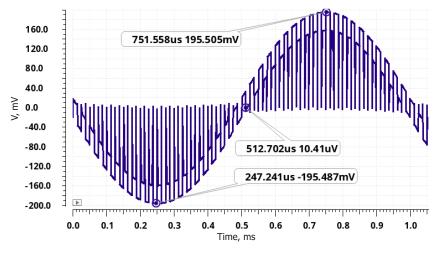

Fig. 6. Chopper amplifier's output signal

amplifiers, chopper amplifiers do not cause noise-folding. This method is based on modulation. The principle of operation is that the voltage Vin goes through the chopper that is driven by a clock at frequency  $f_{ch}$ . Hence, it is transformed to a modulated pulse voltage [11, 20–22]. Later, the modulated signal is amplified along with the input offset. The second chopper acts as a demodulator. It demodulates the input signal to a DC voltage, and concurrently modulates the offset to the odd harmonics of clock frequency that will be removed by a low-pass filter [13, 20–24]. In contrast to auto-zeroing, chopper amplifiers do not need any capacitor, they compensate offset voltage using modulation rather than charge compensation. A basic chopper amplifier is presented in Fig. 5. It consists of two modulators (choppers), a fully-differential opamp, and a Butterworth LPF. As in the previous cases, the value of offset voltage is 10 mV, and it is added as a DC voltage source. The output signal is shown in Fig. 6. The signal looks like a sampled signal due to ripples.

Interestingly, both popular offset-voltage reduction techniques can be used together. This advanced architecture allows us to get the best of each technique.

### **Chopping & auto-zeroing**

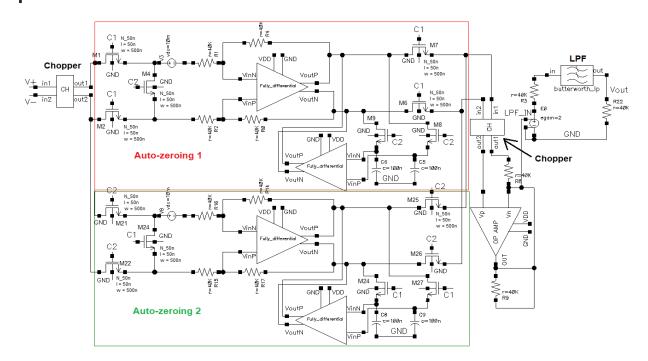

A combination of both chopping and auto-zeroing can be used to achieve better noise performance. That is a more sophisticated configuration despite its complexity, because auto-zeroing part gets rid of the voltage ripples caused by chopping, while chopping gets rid of the noise folding problem caused by auto-zeroing. An example of such topology is provided in Fig. 7.

Fig. 7. Schematic of an amplifier using both chopping and auto-zeroing

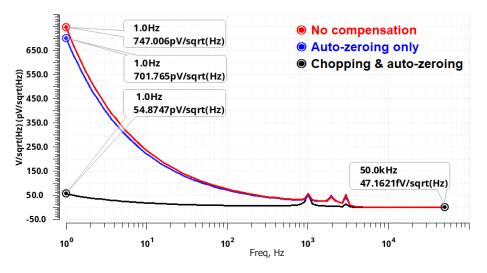

Fig. 8. Schematic of an amplifier using both chopping and auto-zeroing

The circuit consists of two choppers, they are placed at the input and output stages, the first chopper acts as a modulator, while the second chopper acts as a demodulator. Two auto-zeroing amplifiers (they are placed in red and green rectangles) are used between the choppers to further reduce flicker noise and reduce the ripples in the continuous-time signal; their operation can be explained simply by the two-phase nonoverlapping clock signals (C1 and C2). When C1 is one and C2 is zero, the upper auto-zeroing amplifier works in amplification mode while the lower auto-zeroing amplifier compensates the input offset of 10 mV. The feedback loop op-amp senses the voltage difference at the output of the main amplifier, then the capacitors are charged to this value. Later, they are amplified and subtracted from main amplifier's output. In the next clock period (when C1 is zero and C2 is one), the system works in a similar manner.

The lower amplifier operates in amplification mode and the upper amplifier compensates the offset. PSS noise analysis results for the circuit in Fig. 7 are provided in Fig. 8.

Table 1

| Configuration                | Input-referred<br>noise PSD before<br>compensation,<br>nV/√Hz | Input-referred<br>noise PSD before<br>compensation,<br>nV/√Hz | PSRR, dB | CMRR, dB |  |

|------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|----------|----------|--|

| Auto-zeroing (AZ)            | 9.3                                                           | 2.5                                                           | 104      | 98       |  |

| Continuous-time auto-zeroing | 9.4                                                           | 0.02                                                          | 103      | 97       |  |

| Chopping                     | 337                                                           | 4.5                                                           | 116      | 110      |  |

| Chopping & auto-zeroing      | 0.74                                                          | 0.054                                                         | 112      | 106      |  |

## Input-referred noise PSD, PSRR and CMRR

Table 2

## Comparison of the best performing circuit (chopping & auto-zeroing) with previous works

| Parameters                   | This<br>work<br>2021 | [2]<br>2015 | [6]<br>2016 | [7]<br>2015 | [8]<br>2015          | [9]<br>2017 | [11]<br>2015 | [14]<br>2017 | [17]<br>2011 | [20]<br>2010 | [23]<br>2017 |

|------------------------------|----------------------|-------------|-------------|-------------|----------------------|-------------|--------------|--------------|--------------|--------------|--------------|

| Bandwidth,<br>MHz            | 47                   | 2.8         | 10          | 10.3        | 3.1                  | 43          | 0.329        | 1.5          | _            | _            | 30           |

| Bias current,<br>µA          | 4.6×10 <sup>-5</sup> | 420         | 5×10-5      | _           | 1.5×10 <sup>-5</sup> | _           | _            | _            | 175          | _            | _            |

| Chopping<br>frequency, kHz   | 20                   | _           | 150         | 10          | 800                  | 500         | 500          | 1            | _            | 10           | _            |

| CMOS<br>technology µm        | 0.05                 | 0.5         | 0.6         | 0.045       | 0.18                 | 0.18        | 0.028        | 0.18         | 0.18         | 0.18         | 0.18         |

| CMRR, dB                     | 106.6                | 123         | > 120       | _           | 145                  | —           | 70           | _            | 90           | _            | _            |

| Voltage noise<br>PSD, nV/√Hz | 0.05                 | 90          | 6.5         | 2.54        | 6.8                  | 3.5         | 27           | 200          | 15           | 179          | _            |

| Maximum<br>VOS, μV           | 10.4                 | 90          | -           | _           | _                    | _           | _            | _            | 15           | _            | 1296         |

| PSRR, dB                     | 112.6                | _           | > 120       | _           | 150                  | _           | 68           | 131          | 88           | _            | _            |

| Supply<br>voltage, V         | 1                    | 5           | 5.5         | 1           | 60                   | 5           | 0.9          | 1.8          | 3.3          | 1.8          | 1.2          |

## Results

There are multiple metrics that are commonly mentioned in datasheets to evaluate the performance of operational amplifiers: power supply rejection ratio (PSRR), common-mode rejection ratio (CMRR) and input-referred noise power spectral density. These parameters are provided in Table 1. PSRR and CMRR can be obtained using these formulas:

$$PSRR = \frac{\Delta V_{DD}}{\Delta V_{OS}},$$

(1)

$$CMRR = \frac{\Delta V_{CM}}{\Delta V_{OS}},$$

(2)

where  $V_{CM}$  is the common-mode voltage;  $V_{OS}$  is the offset voltage and  $V_{DD}$  is the drain supply voltage (equal to 1 V in the proposed circuits). Additionally, the thermal performance was analyzed, the operational amplifiers work properly in the temperature range of -40 °C to 85 °C.

The results obtained in this work are compared with the existing works in Table 2.

### Conclusion

Four zero-drift operational amplifiers were realized and compared. The operational amplifiers were simulated using Cadence Virtuoso software. The Periodic Steady State (PSS) analysis results showed that the proposed techniques are an effective way to reduce the input offset voltage and flicker (1/f) noise. Two operational amplifiers used in this work have a gain-bandwidth product (GBWP) of 47 MHz and 493 MHz, and an open-loop gain of 69.78 dB and 47 dB, respectively. The clock frequency of 20 kHz was chosen for all the circuits. In short, chopper amplifier and continuous-time auto-zeroing amplifier are reducing the flicker noise and input offset voltage more effectively. Chopper amplifier reduces flicker noise from 337 nV/ $\sqrt{Hz}$  to 4.5 nV/ $\sqrt{Hz}$ , in other words by approximately 7500 %, while continuous-time auto-zeroing amplifier reduces flicker noise from 9.4 nV/ $\sqrt{Hz}$  to 0.02 nV/ $\sqrt{Hz}$ , that is by 47000 %. But taking into account the simplicity, chopper amplifier is the best configuration. Nevertheless, choosing an operational amplifier for a certain application does not depend only on its flicker noise and offset voltage reduction capability. For instance, in continuous-time applications such as in analog-to-digital converters, continuous-time auto-zeroing amplifier can be used despite its humble qualities when compared to other more sophisticated amplifiers.

#### Acknowledgment

I would like to thank my parents for their never ending support. Special thanks to my dearest friend (Nikolai Kirichenko) for his help throughout my studies in St. Petersburg, Russia. Finally, I want to extend my thanks to the editors of this journal for taking time to review my work.

#### REFERENCES

1. **Balashov E.V., Ivanov N.V., Korotkov A.S.** SOI instrumentation amplifier for high-temperature applications. *2020 IEEE East-West Design and Test Symposium (EWDTS*), Varna, Bulgaria, 2020. IEEE, 2020, Pp. 1–4. DOI: 10.1109/EWDTS50664.2020.9224893

2. Balashov E.V., Ivanov N.V., Akhmetov D.B., Korotkov A.S. High-temperature instrumentation amplifier. *Nanoindustry Journal*, 2020, Iss. 96 (3), Pp. 160–163. (rus)

3. Baker R.J. CMOS: Circuit design, layout, and simulation. 3rd ed., IEEE Press, 2010, Pp. 773–908.

4. **Bortun N., Stan M.N., Brezeanu G.** High precision bidirectional chopper amplifier with extended common mode input voltage range. *International Semiconductor Conference (CAS)*, Sinaia, Romania, 2015. IEEE, 2015, Pp. 297–300. DOI: 10.1109/SMICND.2015.7355237

5. Carusone T.C., Johns D.A., Martin K.W. Analog integrated circuit design. 2<sup>nd</sup> ed., Wiley, 2011, Pp. 242–293.

6. Duwe M., Chen T. Offset correction of low power, high precision op amp using digital assist for biomedical applications. *2012 IEEE International Symposium on Circuits and Systems (ISCAS)*, Seoul, South Korea, 2012. IEEE, 2012, Pp. 850–853. DOI: 10.1109/ISCAS.2012.6272175

7. Huijsing J. Operational amplifiers theory and design, 2<sup>nd</sup> ed., Springer Science+Business, Delft, 2011, Pp. 351–412.

8. **Ivanov V., Shaik M.** A 5.1 A 10 MHz-bandwidth 4µs-large-signal-settling 6.5 nV/√Hz-noise 2µV-offset chopper operational amplifier. *2016 IEEE International Solid-State Circuits Conference (ISSCC)*, San Francisco, USA, 2016. IEEE, 2016, Pp. 88–89. DOI: 10.1109/ISSCC.2016.7417920

9. Kuang X., Wang T., Fan F. The design of low noise chopper operational amplifier with inverter. *2015 IEEE 16<sup>th</sup> International Conference on Communication Technology (ICCT)*, Hangzhou, China, 2015. IEEE, 2016, Pp. 568–571. DOI: 10.1109/ICCT.2015.7399903

10. **Kusuda Y.** A 60 V auto-zero and chopper operational amplifier with 800 kHz interleaved clocks and input bias current trimming. *IEEE Journal of Solid-State Circuits*, 2015, Vol. 50, Issue 12, Pp. 2804–2813. DOI: 10.1109/JSSC.2015.2456891

11. Mai T., Schmid K., Rober J., Hagelauer A., Weigel R. A fully differential operational amplifier using a new chopping technique and low-voltage input devices. 2017 24<sup>th</sup> IEEE International Conference on Electronics, Circuits and Systems (ICECS), Batumi, Georgia, 2017. IEEE, 2018, Pp. 74–77. DOI: 10.1109/ICE-CS.2017.8292081

12. Pipino A., Pezzotta A., Resta F., De Matteis M., Baschirotto A. A rail-to-rail-input chopper instrumentation amplifier in 28nm CMOS. *2015 IEEE International Conference on Electronics, Circuits, and Systems* (*ICECS*), Cairo, Egypt, 2015. IEEE, 2016, Pp. 73–76. DOI: 10.1109/ICECS.2015.7440252

13. **Prokop R.** Dynamic input offset auto-compensation of continuously working opamp. 2013 36<sup>th</sup> International Conference on Telecommunications and Signal Processing (TSP), Rome, Italy, 2013. IEEE, 2013, Pp. 440–443. DOI: 10.1109/TSP.2013.6613970

14. **Prokop R., Novak P., Musil V.** Bulk driven offset compensation for continuous time opamp operation. *Proceedings of the 15<sup>th</sup> International Scientific and Applied Science Conference*, Sofia, Bulgaria, 2006. TU-SOFIA, 2006, Pp. 26–29.

15. **Raghuveer V., Balasubramanian K., Sudhakar S.** A 2μV low offset, 130 dB high gain continuous autozero operational amplifier. *2017 International Conference on Communication and Signal Processing (ICCSP)*, Chennai, India, 2017. IEEE, 2018, Pp. 1715–1718. DOI: 10.1109/ICCSP.2017.8286685

16. Shukla G., Srivastava N., Shadab A. DC offset voltage reduction in cascaded instrumentation amplifier. 2013 Students Conference on Engineering and Systems (SCES), Allahabad, India, 2013. IEEE, 2013, Pp. 1–5. DOI: 10.1109/SCES.2013.6547579

17. Singh R., Audet Y., Gagnon Y., Savaria Y., Boulais É., Meunier M. A laser-trimmed rail-to-rail precision CMOS operational amplifier. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 2011, Vol. 58, No. 2, Pp. 75–79. DOI: 10.1109/TCSII.2010.2104011

18. Wu R., Huijsin J.H., Makinwa K.A.A. Precision instrumentation amplifiers and read-out integrated circuits. New York: Springer, 2013, Pp. 21–48.

19. Xu J., Nguyen A.T., Luu D.K., Drealan M., Yang Z. Noise optimization techniques for switched-capacitor based neural interfaces. *IEEE Transactions on Biomedical Circuits and Systems*, 2020, Vol. 14, No. 5, Pp. 1024–1035. DOI: 10.1109/TBCAS.2020.3016738

20. Yang X., Yang J., Lin L., Ling C. Low-power low-noise CMOS chopper amplifier. *2010 International Conference on Anti-Counterfeiting, Security and Identification*, Chengdu, China, 2010. IEEE, 2010, Pp. 83–84. DOI: 10.1109/ICASID.2010.5551831

21. Yeh C., Huang J., Wu P., Tsai H., Juang Y. A low power and low noise CMOS chopper amplifier for use in capacitive type accelerometer. *2016 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS)*, Jeju, South Korea, 2016. IEEE, 2017, Pp. 642–645. DOI: 10.1109/APCCAS.2016.7804072

22. Yong X., Fei Z., Zheng S., Yuanliang W. Design of novel chopper stabilized rail-to-rail operational amplifier. *2015 IEEE 11<sup>th</sup> International Conference on ASIC (ASICON)*, Chengdu, China, 2015. IEEE, 2016, Pp. 1–4. DOI: 10.1109/ASICON.2015.7516988

23. **Zhong X., Bermak A., Tsui C.** A low-offset dynamic comparator with area-efficient and low-power offset cancellation. *2017 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC)*, Abu Dhabi, United Arab Emirates, 2017. IEEE, 2017, Pp. 1–6. DOI: 10.1109/VLSI-SoC.2017.8203481

24. **Zhou Y., Zhao M., Dong Y., Wu X., Tang L.** A low-power low-noise biomedical instrumentation amplifier using novel ripple-reduction technique. *2018 IEEE Biomedical Circuits and Systems Conference (BioCAS)*. Cleveland, USA, 2018. IEEE, 2018. Pp. 1–4. DOI: 10.1109/BIOCAS.2018.8584744

Received 26.08.2021.

### СПИСОК ЛИТЕРАТУРЫ

1. Balashov E.V., Ivanov N.V., Korotkov A.S. SOI instrumentation amplifier for high-temperature applications // 2020 IEEE East-West Design and Test Symp. Varna, Bulgaria, 2020. IEEE, 2020. Pp. 1–4. DOI: 10.1109/EWDTS50664.2020.9224893

2. Балашов Е.В., Иванов Н.В., Ахметов Д.Б., Коротков А.С. Высокотемпературный инструментальный усилитель // Наноиндустрия. 2020. Вып. 96 (3). С. 160–163.

3. Baker R.J. CMOS: circuit design, layout, and simulation. 3<sup>rd</sup> ed. IEEE Press, 2010. Pp. 773–908.

4. **Bortun N., Stan M.N., Brezeanu G.** High precision bidirectional chopper amplifier with extended common mode input voltage range // Internat. Semiconductor Conf. (CAS). Sinaia, Romania, 2015. IEEE, 2015. Pp. 297–300. DOI: 10.1109/SMICND.2015.7355237

5. Carusone T.C., Johns D.A., Martin K.W. Analog integrated circuit design. 2<sup>nd</sup> ed. Wiley, 2011. Pp. 242–293.

6. **Duwe M., Chen T.** Offset correction of low power, high precision op amp using digital assist for biomedical applications // 2012 IEEE Internat. Symp. on Circuits and Systems. Seoul, South Korea, 2012. IEEE, 2012. Pp. 850–853. DOI: 10.1109/ISCAS.2012.6272175

7. **Huijsing J.** Operational amplifiers theory and design. 2<sup>nd</sup> ed. Delft: Springer Science+Business, 2011. Pp. 351–412.

8. **Ivanov V., Shaik M.** A 5.1 A 10 MHz-bandwidth 4 $\mu$ s-large-signal-settling 6.5 nV/ $\sqrt{Hz}$ -noise 2 $\mu$ V-offset chopper operational amplifier // 2016 IEEE Internat. Solid-State Circuits Conf. San Francisco, USA, 2016. IEEE, 2016. Pp. 88–89. DOI: 10.1109/ISSCC.2016.7417920

9. Kuang X., Wang T., Fan F. The design of low noise chopper operational amplifier with inverter // 2015 IEEE 16<sup>th</sup> Internat. Conf. on Communication Technology. Hangzhou, China, 2015. IEEE, 2016. Pp. 568–571. DOI: 10.1109/ICCT.2015.7399903

10. Kusuda Y. A 60 V auto-zero and chopper operational amplifier with 800 kHz interleaved clocks and input bias current trimming // IEEE J. of Solid-State Circuits. 2015. Vol. 50. Iss. 12. Pp. 2804–2813. DOI: 10.1109/ JSSC.2015.2456891

11. Mai T., Schmid K., Rober J., Hagelauer A., Weigel R. A fully differential operational amplifier using a new chopping technique and low-voltage input devices // 2017 24<sup>th</sup> IEEE Internat. Conf. on Electronics, Circuits and Systems. Batumi, Georgia, 2017. IEEE, 2018. Pp. 74–77. DOI: 10.1109/ICECS.2017.8292081

12. Pipino A., Pezzotta A., Resta F., De Matteis M., Baschirotto A. A rail-to-rail-input chopper instrumentation amplifier in 28nm CMOS // 2015 IEEE Internat. Conf. on Electronics, Circuits, and Systems. Cairo, Egypt, 2015. IEEE, 2016. Pp. 73–76. DOI: 10.1109/ICECS.2015.7440252

13. **Prokop R.** Dynamic input offset auto-compensation of continuously working opamp // 2013 36<sup>th</sup> Internat. Conf. on Telecommunications and Signal Processing. Rome, Italy, 2013. IEEE, 2013. Pp. 440–443. DOI: 10.1109/TSP.2013.6613970

14. **Prokop R., Novak P., Musil V.** Bulk driven offset compensation for continuous time opamp operation // Proc. of the 15<sup>th</sup> Internat. Scientific and Applied Science Conf. Sofia, Bulgaria, 2006. TU-SOFIA, 2006. Pp. 26–29.

15. **Raghuveer V., Balasubramanian K., Sudhakar S.** A 2μV low offset, 130 dB high gain continuous autozero operational amplifier // 2017 Internat. Conf. on Communication and Signal Processing. Chennai, India, 2017. IEEE, 2018. Pp. 1715–1718. DOI: 10.1109/ICCSP.2017.8286685 16. Shukla G., Srivastava N., Shadab A. DC offset voltage reduction in cascaded instrumentation amplifier // 2013 Students Conf. on Engineering and Systems. Allahabad, India, 2013. IEEE, 2013. Pp. 1–5. DOI: 10.1109/SCES.2013.6547579

17. Singh R., Audet Y., Gagnon Y., Savaria Y., Boulais É., Meunier M. A laser-trimmed rail-to-rail precision CMOS operational amplifier // IEEE Transactions on Circuits and Systems II: Express Briefs. 2011. Vol. 58. No. 2. Pp. 75–79. DOI: 10.1109/TCSII.2010.2104011

18. Wu R., Huijsin J.H., Makinwa K.A.A. Precision instrumentation amplifiers and read-out integrated circuits. New York: Springer, 2013. Pp. 21–48.

19. Xu J., Nguyen A.T., Luu D.K., Drealan M., Yang Z. Noise optimization techniques for switched-capacitor based neural interfaces // IEEE Transactions on Biomedical Circuits and Systems. 2020. Vol. 14. No. 5. Pp. 1024–1035. DOI: 10.1109/TBCAS.2020.3016738

20. Yang X., Yang J., Lin L., Ling C. Low-power low-noise CMOS chopper amplifier // 2010 Internat. Conf. on Anti-Counterfeiting, Security and Identification. Chengdu, China, 2010. IEEE, 2010. Pp. 83–84. DOI: 10.1109/ICASID.2010.5551831

21. Yeh C., Huang J., Wu P., Tsai H., Juang Y. A low power and low noise CMOS chopper amplifier for use in capacitive type accelerometer // 2016 IEEE Asia Pacific Conf. on Circuits and Systems. Jeju, South Korea, 2016. IEEE, 2017. Pp. 642–645. DOI: 10.1109/APCCAS.2016.7804072

22. Yong X., Fei Z., Zheng S., Yuanliang W. Design of novel chopper stabilized rail-to-rail operational amplifier // 2015 IEEE 11<sup>th</sup> Internat. Conf. on ASIC. Chengdu, China, 2015. IEEE, 2016. Pp. 1–4. DOI: 10.1109/ ASICON.2015.7516988

23. Zhong X., Bermak A., Tsui C. A low-offset dynamic comparator with area-efficient and low-power offset cancellation // 2017 IFIP/IEEE Internat. Conf. on Very Large Scale Integration. Abu Dhabi, United Arab Emirates, 2017. IEEE, 2017. Pp. 1–6. DOI: 10.1109/VLSI-SoC.2017.8203481

24. Zhou Y., Zhao M., Dong Y., Wu X., Tang L. A low-power low-noise biomedical instrumentation amplifier using novel ripple-reduction technique // 2018 IEEE Biomedical Circuits and Systems Conference (Bio-CAS). Cleveland, USA, 2018. IEEE, 2018. Pp. 1–4. DOI: 10.1109/BIOCAS.2018.8584744

Статья поступила в редакцию 26.08.2021.

### THE AUTHORS / СВЕДЕНИЯ ОБ АВТОРАХ

**Assim Ara Abdulsatar Ассим Ара Абдулсатар** E-mail: araabdulsattar@gmail.com

Balashov Evgenii V. Балашов Евгений Владимирович E-mail: balashov\_ev@mail.ru

© Санкт-Петербургский политехнический университет Петра Великого, 2021