# Санкт-Петербургский политехнический университет Петра Великого

# Институт физики, нанотехнологий и телекоммуникаций

На правах рукописи

# Буданов Дмитрий Олегович

# Синтез и реализация параллельного аналого-цифрового преобразователя со сниженными потерями в эффективной разрядности

Направление подготовки

11.06.01 «Электроника, радиотехника и системы связи»

Код и наименование

Направленность

11.06.01 01 Радиотехника, в том числе системы и устройства телевидения

Код и наименование

# НАУЧНЫЙ ДОКЛАД

об основных результатах научно-квалификационной работы (диссертации)

Автор работы: Буданов Дмитрий

Олегович

Научный руководитель: проф., д.т.н. Коротков Александр Станиславович Научно-квалификационная работа выполнена в Высшей школе прикладной физики и космических технологий (ВШПФиКТ) Института физики, нанотехнологий и телекоммуникаций федерального государственного автономного образовательного учреждения высшего образования «Санкт-Петербургский политехнический университет Петра Великого»

Директор ВШПФиКТ: Величко Елена Николаевна

к.т.н., доцент

Научный руководитель: Коротков Александр

Станиславович, д.т.н., проф.

Рецензент: Теленков Михаил Валерьевич,

канд. техн. н-к, ООО «АСХ»,

ведущий специалист

С научным докладом можно ознакомиться в библиотеке ФГАОУ ВО «Санкт-Петербургский политехнический университет Петра Великого» и на сайте Электронной библиотеки СПбПУ по адресу: http://elib.spbstu.ru

#### ОБЩАЯ ХАРАКТЕРИСТИКА РАБОТЫ

#### Актуальность работы

Аналого-цифровые преобразователи (АЦП) являются неотъемлемой интерфейсной частью устройств, выполняющих цифровую обработку сигналов в современных системах инфокоммуникаций. Одним из ключевых параметров подобных систем является скорость обработки информации. При этом наибольшим быстродействием обладают параллельные аналогоцифровые преобразователи. Отличия от расчетных значений уровней опорного напряжения компараторов вследствие неидеальности элементов схемы и нарушения монотонности термометрического кода, подаваемого с выходов массива компараторов на шифратор приводят к снижению эффективной разрядности.

В рамках данной работы рассматриваются вопросы, связанные с синтезом и реализацией параллельного аналого-цифрового преобразователя со сниженными потерями в эффективной разрядности.

#### Цель и задачи исследования

Цель работы — синтез и реализация параллельного аналого-цифрового преобразователя со сниженными потерями в эффективной разрядности.

Для достижения данной цели в ходе работы решаются следующие задачи:

- Обзор методов снижения потерь в эффективной разрядности;

- Разработка аналоговой части АЦП;

- Разработка цифровой части АЦП;

- Схемотехническая реализация и моделирование АЦП;

#### Научная новизна

Впервые предложена методика синтеза параллельного аналогоцифрового преобразователя, позволяющая снизить потери в эффективной разрядности и дифференциальную нелинейность при сохранении скорости преобразования.

# Теоретическая и практическая значимость

Предложенная методика синтеза параллельных АЦП позволяет реализовывать преобразователи со сниженными потерями в эффективной разрядности и сниженной дифференциальной нелинейностью, что упрощает схемное решение преобразователя и позволяет снизить занимаемую на кристалле площадь за счет отсутствия необходимости в схемах коррекции.

Применение предложенной снижает влияние разброса номиналов и паразитных параметров элементов схемы на результат преобразования и, как следствие, на эффективную разрядность.

# Апробация работы

Результаты работы представлены на двух межвузовских научных конференциях «Недели Науки СПбГПУ» 2011, 2012, на научно-практической конференции с международным участием «Неделя Науки СПбГПУ» 2013, на международном научно-практическом семинаре «Проблемы современной аналоговой микросхемотехники» 2013, ИСОиП (филиал) ДГТУ, на VI всероссийской научно-практической конференции Проблемы разработки перспективных микро- и наноэлектронных систем – 2014 (МЭС-2014), на научном форуме с международным участием «Неделя Науки СПбПУ» 2015, на XVIII конференции молодых ученых «Навигация и управление движением» с международным участием «АО «Концерн «ЦНИИ «Электроприбор» 2016, на XIX конференции молодых ученых (с международным участием) «Навигация «AO «Концерн «ЦНИИ И управление движением»

«Электроприбор» 2017, на международной конференции IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering 2018.

## Публикации

- 1. Д.О. Буданов, Д.В. Морозов, "Методы увеличения эффективной разрядности параллельных аналого-цифровых преобразователей" / В сб. материалов межвузовской научной конференции «ХL Неделя науки СПбГПУ» 5-10 декабря 2011 года, ч. ІХ, СПб.: СПбГПУ, 2011. с.44-46.

- 2. Д.О. Буданов, Д.В. Морозов, "Компаратор для параллельного АЦП" / В сб. материалов межвузовской научной конференции «XLI Неделя науки СПбГПУ» 3-8 декабря 2012 года, ч. IX, СПб.: СПбГПУ, 2012. с.33-35.

- 3. Д. В. Морозов, Д. О. Буданов, "Шифратор термометрического кода в прямой двоичной код" / Научно-технические ведомости СПбГПУ Информатика. Телекоммуникации. Управление, 1 (164), 2013, с. 87–92.

- 4. Д. О. Буданов, "Моделирование восьмиразрядного параллельного АЦП с массивом избыточных компараторов", / В сб. материалов X Международного научно-практического семинара «Проблемы современной аналоговой микросхемотехники», Шахты, 1-2 октября 2013 года, ч. І, Шахты: ИСОиП (филиал) ДГТУ, 2013, с. 69-72.

- 5. Д.О. Буданов, Д.В. Морозов, "Моделирование восьмиразрядного параллельного АЦП с учетом топологии кристалла" / В сб. материалов межвузовской научной конференции «Неделя науки СПбГПУ», 2-7 декабря 2013 года, ИФНиТ, ч. I, СПб.: СПбГПУ, 2014. с.137-139.

- 6. Д.О. Буданов, М.М. Пилипко, Д.В. Морозов, "Восьмиразрядный параллельный АЦП со сниженной дифференциальной нелинейностью" / Проблемы разработки перспективных микро- и наноэлектронных систем 2014. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2014. ч. III. с. 35-38.

- 7. Д.О. Буданов, Д.В. Морозов, "Измерение характеристик аналого-цифровых преобразователей" / Научный форум с международным участием

- «Неделя науки СПбПУ» 1-6 декабря 2014 года, Институт физики, нанотехнологий и телекоммуникаций СПбПУ, СПб.: СПбПУ, 2015, с 148 -151.

- 8. D. O. Budanov, D. V. Morozov, M. M. Pilipko, "An 8-Bit Flash ADC With Reduced DNL" / Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2015. № 3. с. 10.

- 9. Е. Л. Фертикова, Д. О. Буданов, "Шифраторы термометрического кода" / В сб.: Неделя науки СПбПУ материалы научного форума с международным участием. Институт физики, нанотехнологий и телекоммуникаций; В.Э. Гасумянц, Д.Д. Каров ответственные редакторы. 2015. с. 201-204.

- 10. А. Коротков, Д. Морозов, М. Пилипко, И. Пятак, Д. Буданов, "Аналогоцифровые преобразователи для беспроводных систем связи: опыт разработки" / Электроника: Наука, технология, бизнес. 2016. № 2 (152). С. 40-47.

- Е. Л. Фертикова, Д. О. Буданов, "Ошибки термометрического кода" / В 11. конференции сб.: Неделя науки СПбПУ Материалы научной cмеждународным участием. Институт физики, нанотехнологий И телекоммуникаций. 2016. с. 118-120.

- 12. Е. Л. Фертикова, Д. О. Буданов, "Ошибки термометрического кода в параллельных АЦП" / В сб.: Неделя науки СПбПУ Материалы научной конференции с международным участием. Лучшие доклады. 2016. С. 106-110.

- 13. Д.О. Буданов, Д.В. Морозов, М.М. Пилипко, "Восьмиразрядный параллельный аналого-цифровой преобразователь с массивом избыточных компараторов" / Радиотехника и электроника. 2017. Т. 62. № 4. с. 399-410.

- 14. М.М. Пилипко, Д.В. Морозов, Д.О. Буданов, "Сравнительный анализ КМОП-схем шифраторов термометрического кода в прямой двоичный код для параллельных АЦП в интегральном исполнении" / Микроэлектроника. 2017. Т. 46. № 1. с. 50-60.

- 15. D. O. Budanov, D. V. Morozov, M. M. Pilipko, "An 8-bit Flash Analog-to-Digital Converter With An Array Of Redundant Comparators" / Journal of Communications Technology and Electronics. 2017. Vol. 62. № 4. pp. 421-431.

- 16. M. M. Pilipko, D. V. Morozov, D. O. Budanov, "Comparative Analysis Of CMOS Circuits Of A Thermometer-to-Binary Encoder For Integrated Flash Analog-to-Digital Converters" / Russian Microelectronics. 2017. Vol. 46. № 1. pp. 45-54.

- 17. D. O. Budanov, M. M. Pilipko, D. V. Morozov, "Encoders For Flash Analog-to-Digital Converters" / 2018 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), January 29 February 1, 2018, St. Petersburg, Russia, pp. 173-177.

# СОДЕРЖАНИЕ РАБОТЫ

| Введение                                                       | 9      |

|----------------------------------------------------------------|--------|

| Цель и задачи                                                  | 11     |

| Обзор методов снижения потерь в эффективной разрядности        | 12     |

| Разработка аналоговой части АЦП                                | 16     |

| Разработка цифровой части АЦП                                  | 19     |

| Схемотехническая реализация и моделирование АЦП                | 22     |

| Список использованных источников                               | 32     |

| Список работ, опубликованных по теме научно-квалификационной р | работы |

| (диссертации)                                                  | 33     |

#### Введение

Аналого-цифровой (АЦП) преобразователь устройство, преобразующее входной аналоговый сигнал в цифровой (двоичный) код. Аналого-цифровые преобразователи являются неотъемлемой интерфейсной частью устройств, выполняющих цифровую обработку сигналов. Различают следующие архитектуры АЦП: последовательного приближения и счета, сигма-дельта и параллельного преобразования (параллельные). Скорость передачи информации В современных системах инфокоммуникаций представляет критичный параметр. При этом наибольшим быстродействием обладают параллельные АЦП, максимальная скорость преобразования которых может достигать единиц гигаотсчетов в секунду. Практический интерес представляют преобразователи с разрядностью восемь и более бит.

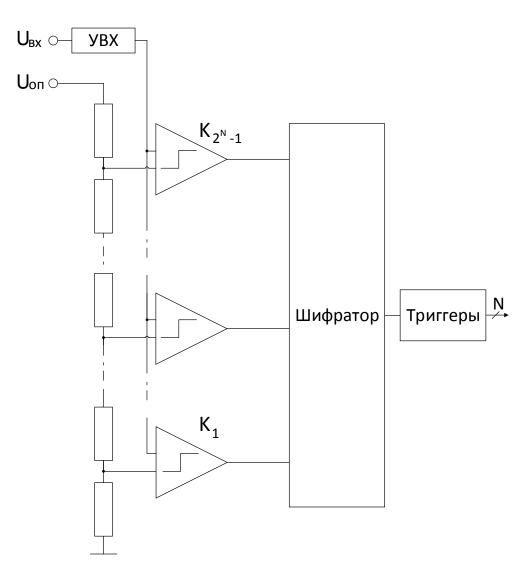

Параллельный аналого-цифровой преобразователь с разрядностью N бит (рисунок 1) содержит: устройство выборки-и-хранения (УВХ), делитель  $2^{N}-1$ напряжения, компаратор, уровней опорного шифратор термометрического кода в прямой двоичный код и выходные триггеры. Входной сигнал  $U_{\rm RX}$  подается на устройство выборки-и-хранения, которое протяжении обеспечивает постоянство сигнала на всего времени преобразования. Сигнал с выхода УВХ поступает на компараторы, которые обеспечивают сравнение с  $2^N - 1$  уровнями опорного напряжения  $U_{\text{ОП}}$ . Если опорное напряжение компаратора меньше напряжения входного сигнала, то на выходе компаратора устанавливается напряжение высокого уровня, соответствующее логической единице. Таким образом, на выходах массива компараторов формируется термометрический код, который преобразуется в двоичный код посредством шифратора. Массив триггеров на выходе шифратора позволяет синхронизировать АЦП с последующими устройствами уменьшить влияние задержек в элементах схемы на результат преобразования.

Рисунок 1 – Структура параллельного АЦП

# Цель и задачи

Цель работы — синтез и реализация параллельного аналого-цифрового преобразователя со сниженными потерями в эффективной разрядности.

Для достижения данной цели в ходе работы решаются следующие задачи:

- Обзор методов снижения потерь в эффективной разрядности;

- Разработка аналоговой части АЦП;

- Разработка цифровой части АЦП;

- Схемотехническая реализация и моделирование АЦП;

## Обзор методов снижения потерь в эффективной разрядности

Основной вклад в потери в эффективной разрядности вносят отличия от расчетных уровней опорного напряжения компараторов и нарушения монотонности термометрического кода, поступающего на шифратор. Уход уровней опорного напряжения от расчетных значений вызван неидеальностью элементов схемы АЦП (резистивной делительной цепочки, компараторов и т.д.). Причем, как показано в [1] точность преобразования параллельного АЦП в первую очередь ограничена точностью изготовления компараторов, а уже затем резистивной делительной цепочки. Архитектура параллельных АЦП может быть модифицирована для снижения влияния неидеальностей элементов на результат преобразования [2]. Нарушения монотонности термометрического кода, подаваемого с выходов массива компараторов на шифратор происходят вследствие различного времени преобразования компараторов, выполняющих сравнение с различными уровнями опорного напряжения, влияния паразитных параметров элементов соединительных проводов. Для коррекции основных видов ошибок модифицированные немонотонности ΜΟΓΥΤ быть применены схемы шифраторов.

Обобщая сказанное, можно предложить следующие способы снижения потерь в эффективной разрядности:

- Использование модифицированных архитектур параллельных АЦП;

- Снижение влияния немонотонности термометрического кода на результат преобразования АЦП.

Для снижения потерь в эффективной разрядности вследствие ухода уровней опорного напряжения компараторов от расчетных значений могут быть применены следующие модификации архитектуры параллельного аналого-цифрового преобразователя:

• Увеличение размеров МОП-транзисторов дифференциальной пары компаратора [2];

- Использование интерполяционной архитектуры [1], [3], [4];

- Использование массива избыточных компараторов и схемы калибровки [2], [5].

Потери в эффективной разрядности для шестиразрядного параллельного АЦП без применения рассмотренных модификаций составляют около 2,5 бита [2]. Увеличение размеров МОП-транзисторов дифференциальной пары компаратора приводит к увеличению эффективной разрядности на 0,8 бита по сравнению со схемой без модификаций [2]. Потери в эффективной разрядности для интерполяционной архитектуры шестиразрядного АЦП составляют около 1 бита [1], [4], [6]. Наибольшего снижения потерь в эффективной разрядности, до 0,3 бита, удается достичь при реализации АЦП с архитектурой с массивом избыточных компараторов и схемы калибровки [2]. При этом, с увеличением числа компараторов потери в эффективной разрядности снижаются и при трех компараторох для представления каждого разряда термометрического кода потери в эффективной разрядности малы и не превосходят 0,4 бита. Дальнейшее увеличение числа компараторов приводит к уменьшению потерь не более чем на 0,1 бита [2].

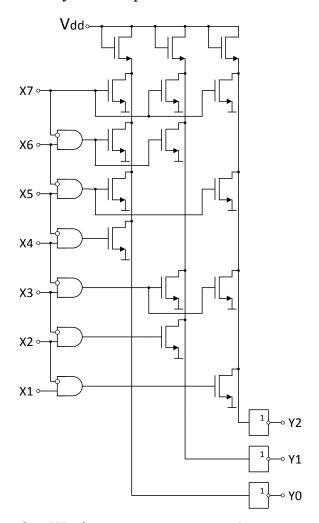

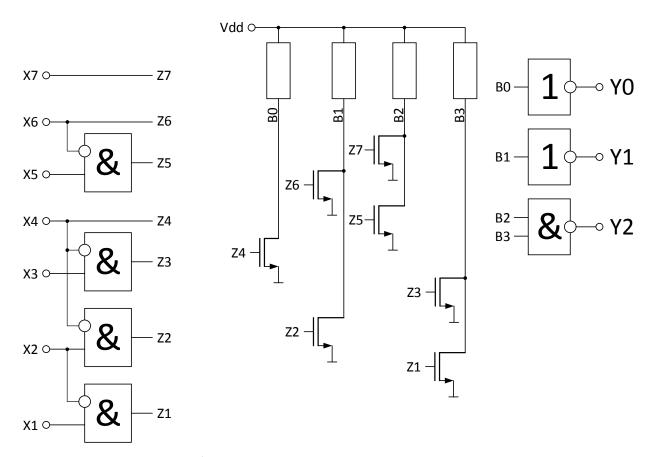

На результат преобразования термометрического кода с выходов массива компараторов ΜΟΓΥΤ оказывать влияние нарушения монотонности термометрического кода. Нарушением монотонности термометрического кода называется комбинация, в которой один и более нулевых разрядов предшествует логическим единицам в более старших разрядах. Нарушением монотонности термометрического кода первого типа является комбинация, в которой нулевой разряд предшествует логическим единицам в более старших разрядах. Нарушением второго типа – в которой два нулевых разряда предшествуют логическим единицам в более старших разрядах и т.д. Например, в шифраторе на основе ROM-архитектуры (рисунок 2), кодовая комбинация 10111 с нарушением монотонности первого типа, получаемая из кодовой комбинации 11111, соответствующей двоичному коду 101, преобразуется первой стадией шифратора в комбинацию 10100. Результатом

преобразования данной комбинации второй стадией шифратора будет двоичный код 111.

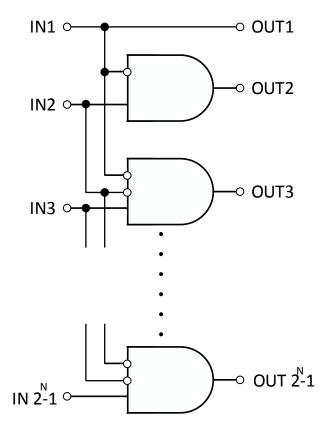

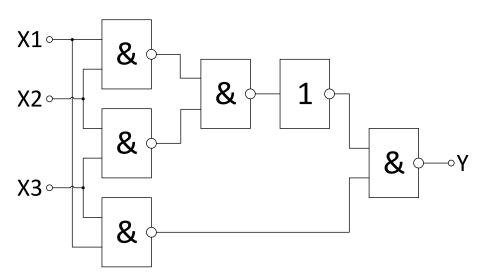

Для устранения влияния нарушения монотонности термометрического кода на результат преобразования в качестве первой стадии шифратора, преобразователя термометрического кода в унитарный, можно применить схему преобразователя термометрического кода в унитарный код, представленную на рисунке 3 [7], в которой используется трехвходовой логический элемент «И» с двумя инверсными входами.

Рисунок 2 – Шифратор на основе ROM-архитектуры

Рисунок 3 — Преобразователь термометрического кода в унитарный с коррекцией ошибок немонотонности термометрического кода первого типа

# Разработка аналоговой части АЦП

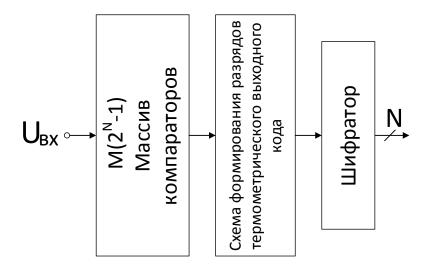

Как было отмечено ранее, наименьшими потерями в эффективной разрядности обладает архитектура параллельного аналого-цифрового преобразователя с массивом избыточных компараторов и схемой калибровки. Однако при этом возникает необходимость изготовления дополнительных структурных блоков, реализуемых, как правило, на микроконтроллере. В работе предлагается использовать схему  $\mathbf{c}$ массивом избыточных компараторов для представления каждого разряда термометрического кода без использования калибровки (рисунок 4). При схемы ДЛЯ шестиразрядного параллельного АЦП потери в эффективной разрядности увеличиваются до 1,3 бит. При этом, данный подход позволяет упростить структуру АЦП, исключить схему калибровки и снизить занимаемую на кристалле площадь.

Таким образом, в *N*-разрядном параллельном АЦП используются массив  $M(2^N-1)$ компараторов из И схема формирования разряда термометрического выходного кода на основе выходных сигналов Mкомпараторов (рисунок 4). Как отмечалось ранее, при M > 3 увеличение числа компараторов снижает потери в эффективной разрядности не более чем на 0,1 бита. В связи представления c этим, ДЛЯ каждого разряда термометрического кода используется M=3 компаратора.

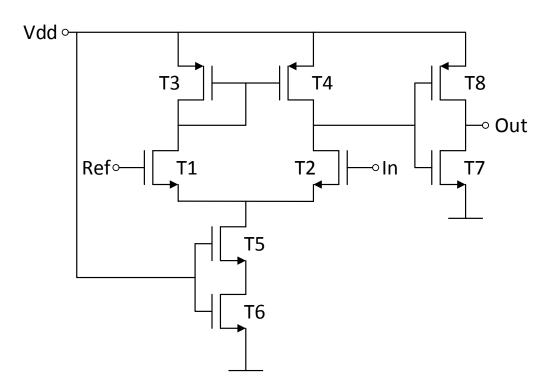

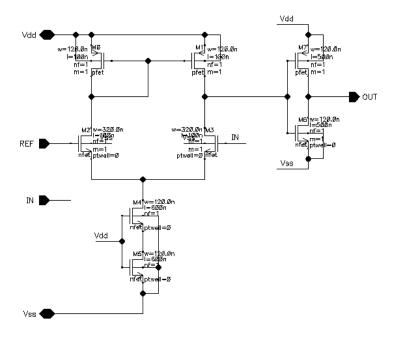

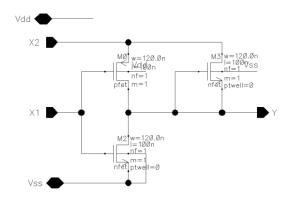

Компаратор реализуется согласно рекомендациям работы [8]. Схема компаратора представлена на рисунке 5. На порт In подается входной сигнал, на порт Ref — опорное напряжение, на порт Vdd — напряжение питания. Выходной сигнал снимается с выхода Out. На затворы транзисторов Т5 и Т6 подается напряжение питания для обеспечения работы транзисторов в режиме насыщения и упрощения схемы путем исключения делителей напряжения. Также дополнительный транзистор в источнике тока позволяет увеличить линейность характеристики преобразования аналого-цифрового преобразователя.

Рисунок 4 — Структура параллельного АЦП с массивом избыточных компараторов

Рисунок 5 – Схема компаратора

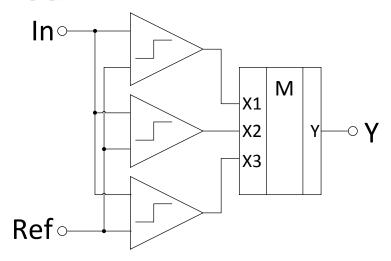

Для формирования каждого разряда термометрического кода используется блок из трех компараторов и мажорирующего элемента (рисунок 6). Сигналы с выходов компараторов подаются на мажорирующий элемент. На выходе мажорирующего элемента будет напряжение высокого уровня, соответствующее логической единице, если на выходах двух и более

компараторов присутствует напряжение, соответствующее логической единице. В обратном случае на выходе мажорирующего элемента будет напряжение низкого уровня, соответствующее логическому нулю (таблица 1). По таблице истинности синтезируется схема мажорирующего элемента (рисунок 7). На входы X1, X2 и X3 подаются сигналы с компараторов, осуществляющих кодирование одного разряда выходного термометрического кода. Сигнал мажорирующего элемента, снимается с выхода Y.

Рисунок 6 — Блок из трех компараторов и мажорирующего элемента для формирования разряда термометрического кода

Рисунок 7 – Схема мажорирующего элемента

$X_1$  $X_2$  $X_3$ Y

Таблица 1 – Таблица истинности мажорирующего элемента

# Разработка цифровой части АЦП

Основным блоком цифровой части параллельного аналого-цифрового преобразователя является шифратор, преобразующий термометрический код с выходов массива компараторов в прямой двоичный код. Различают следующие основные архитектуры шифраторов:

- На основе мультиплексоров;

- На основе древовидной архитектуры (Fat-Tree);

- На основе ROM-архитектуры.

При этом наибольшим быстродействием обладает шифратор на основе ROM-архитектуры [9]. Недостатками данного вида шифраторов являются подверженность влиянию нарушений монотонности термометрического кода и высокая потребляемая мощность. Известны следующие модификации схемы ROM-шифратора, позволяющие снизить указанные недостатки [9]:

- Схема с учетом номеров входных разрядов;

- Схема с реализацией логических функций в массиве МОПтранзисторов;

- Схема на основе КМОП-транзисторов.

На основе совмещения идей синтеза представленных схем для увеличения быстродействия в работе предлагаются следующие модификации:

• Схема с реализацией логических функций в массиве КМОПтранзисторов и дерева в цепи младшего разряда; • Схема с учетом номеров входных разрядов на основе логический элемента  $a \cdot \bar{b}$  с логическим элементом И-НЕ в цепи младшего разряда.

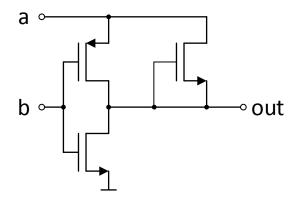

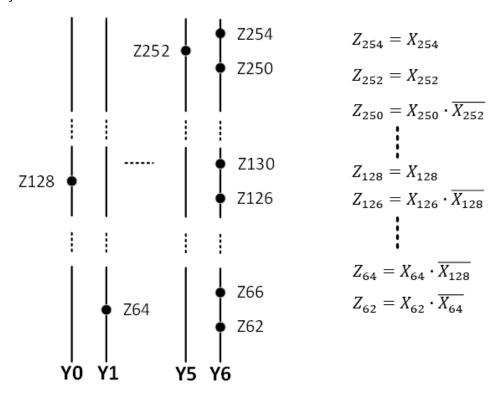

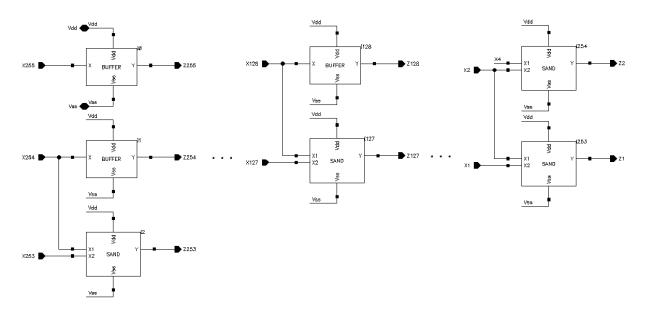

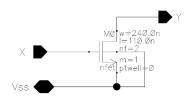

Для реализации в составе восьмиразрядного параллельного АЦП выбирается схема с учетом номеров входных разрядов на основе логического элемента  $a\cdot \bar{b}$  (рисунок 8) с логическим элементом И-НЕ в цепи младшего разряда (рисунок 9) как обладающая наибольшим быстродействием [9]. При этом столбец массива МОП-транзисторов, соответствующий младшему разряду  $Y_{N-1}$  представлен двумя столбцами, сигналы с которых подаются на логический элемент И-НЕ. При увеличении разрядности шифратора аналогично реализованной цепью с двухвходовым логическим элементом И-HE формируется только младший выходной Применение разряд. трехвходового (и более) элемента И-НЕ в выходной цепи приводит к снижению быстродействия схемы шифратора из-за большего времени задержки переключения логического элемента [9]. В данной схеме для формирования промежуточных сигналов  $Z_i$  используется массив логических элементов  $a \cdot \bar{b}$ .

Рисунок 8 — Схема логического элемента  $a\cdot \bar{b}$

Рисунок 9 — Шифратор с учетом номеров входных разрядов на основе логического элемента  $a\cdot \bar{b}$  с логическим элементом И-НЕ в цепи младшего разряда

При этом в N-разрядном шифраторе младший разряд  $Y_{N-1}$  зависит от сигналов  $Z_k$  вспомогательной схемы, имеющих нечетные номера:

$$Y_{N-1} = \sum_{k=0} Z_{2k+1} \tag{1}$$

Сигнал на выходе  $Y_{N-2}$  зависит от сигналов  $Z_k$  с номерами, кратными 2. Сигнал на  $Y_{N-1-i}$  выходе зависит от сигналов вспомогательной схемы с номерами, кратными  $2^i$ . Таким образом, сигналы на выходах шифратора, за исключением младшего разряда определяются формулой:

$$Y_{N-1-i} = \sum_{k=1} Z_{2^i k}$$

для  $i = 1..N$  (2)

Сигналы вспомогательной схемы  $Z_j$  формируются из входных сигналов  $X_n$ , поступающих на вход шифратора следующим образом:

$$Z_{2^{N}-1} = X_{2^{N}-1} \tag{3}$$

$$Z_{2k+1} = X_{2k+1} \cdot \overline{X_{2k+2}} \tag{4}$$

$$Z_{2^{i}k} = X_{2^{i}k}\overline{X_M} \tag{5}$$

где  $X_M$  — ближайший к  $X_{2^ik}$  сигнал с четным номером, расположенный на шине более старшего разряда выходного кода или 0, если такого X не существует. Примеры формирования некоторых значений промежуточных сигналов  $Z_j$  восьмиразрядного шифратор представлены на рисунке 10.

Рисунок 10 – Формирование промежуточных сигналов  $Z_i$

## Схемотехническая реализация и моделирование АЦП

Схемотехническая реализация и моделирование параллельного восьмиразрядного аналого-цифрового преобразователя проводилось при использовании САПР Cadence Virtuoso с использованием библиотеки для 90 нм КМОП-технологии компании Angstrem-T при однополярном напряжении питания 1,2 В.

Компаратор, используемый в разрабатываемом восьмиразрядном параллельном АЦП (рисунок 11), реализуется по схеме рисунка 5. Входной аналоговый сигнал поступает на порт IN, опорное напряжение на порт REF. Напряжение питания подается на порт Vdd. Порт Vss присоединяется к

земляной шине. Результат сравнения считывается с вывода ОUТ. В качестве источника тока используются параллельно включенные транзисторы M4 и M5.

Рисунок 11 – Схема компаратора

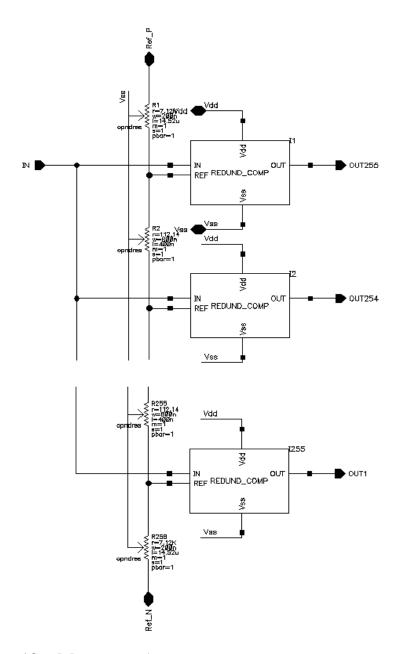

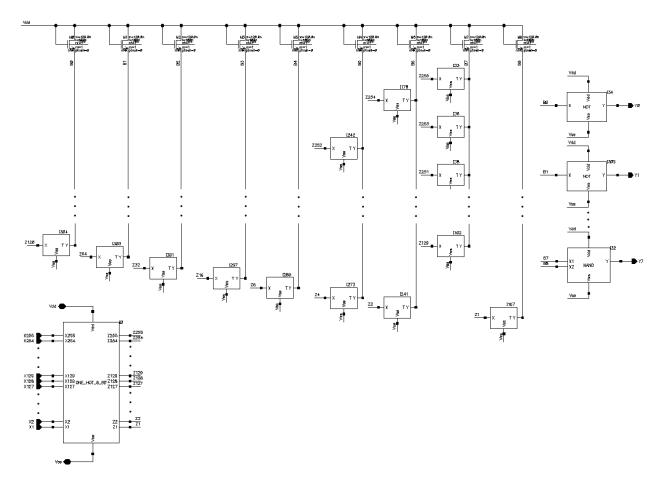

Схемотехническое решение аналоговой части АЦП представлено на рисунке 12. Преобразуемый входной сигнал поступает на порт IN, напряжение питания поступает на порт Vdd. Порт Vss присоединяется к земляной шине. На порты Ref\_P и Ref\_N подаются верхний и нижний уровни опорного напряжения соответственно.

Рисунок 12 — Массив избыточных компараторов и резистивная делительная цепочка параллельного восьмиразрядного АЦП

Схемотехническое решение восьмиразрядного шифратора термометрического кода в прямой двоичный код с учетом номеров входных разрядов на основе логический элемента  $a \cdot \bar{b}$  с логическим элементом И-НЕ в цепи младшего разряда представлено на рисунке 13. Напряжение питания поступает на порт Vdd. Порт Vss присоединяется к земляной шине. Преобразуемый термометрический код с выходов массива компараторов подается на порты X1 - X255, прямой двоичный код, соответствующий данной комбинации, считывается с выходов Y0 - Y7. Блок ONE\_HOT\_8\_BIT

(рисунок 14) преобразует термометрический код с портов X1 — X255 в промежуточные сигналы Z1 — Z255 согласно формулам (3) — (5). Блок BUFFER является буферным элементом из двух последовательно соединенных КМОП-инверторов, блок SAND реализует логическую функцию  $a \cdot \bar{b}$  (рисунок 15). Блок T (рисунок 16) представляет собой ключ.

Рисунок 13 — Восьмиразрядный шифратор термометрического кода в прямой двоичный код

Рисунок 14 – Схема формирования промежуточных сигналов Z1 – Z255

Рисунок 15 – Логический элемент  $a \cdot \bar{b}$

Рисунок 16 – Схема элемента Т

Моделирование временных и мощностных характеристик шифратора проводилось для трех значений температуры при всех возможных граничных условиях (corner-параметрах). Результаты моделирования представлены в таблице 2. В таблицах 3 и 4 представлены результаты моделирования обработки нарушений монотонности термометрического кода первого и второго типа соответственно.

Таблица 2 – Результаты моделирования временных и мощностных параметров

| Corner           | T, <sup>0</sup> C | Задержка по | Задержка по спаду, | Потребляемая   |

|------------------|-------------------|-------------|--------------------|----------------|

|                  |                   | фронту, пс  | пс                 | мощность, мкВт |

|                  | -40               | 83          | 290                | 339            |

| FETS_TT          | 27                | 92          | 272                | 314            |

|                  | 85                | 95          | 279                | 293            |

|                  | -40               | 63          | 178                | 428            |

| FETS_FF          | 27                | 68          | 174                | 398            |

|                  | 85                | 70          | 180                | 374            |

|                  | -40               | 108         | 527                | 266            |

| FETS_SS          | 27                | 122         | 459                | 245            |

|                  | 85                | 127         | 463                | 228            |

|                  | -40               | 82          | 152                | 419            |

| FETS_FS          | 27                | 88          | 152                | 388            |

|                  | 85                | 92          | 157                | 362            |

|                  | -40               | 78          | 844                | 280            |

| FETS_SF          | 27                | 90          | 627                | 259            |

|                  | 85                | 93          | 628                | 242            |

|                  | -40               | 52          | 134                | 490            |

| FETS_FFF         | 27                | 56          | 134                | 458            |

|                  | 85                | 57          | 140                | 432            |

| FETS_SSF         | -40               | 136         | 777                | 228            |

|                  | 27                | 153         | 649                | 209            |

|                  | 85                | 160         | 640                | 194            |

| Среднее значение |                   | 94          | 374                | 326            |

| Макс. значение   |                   | 160         | 844                | 490            |

Таблица 3 – Результаты моделирования обработки нарушений монотонности первого типа

| Правильная комбинация |     | Комбинация с ошибкой | Результат преобразования |     |

|-----------------------|-----|----------------------|--------------------------|-----|

| 11111                 | 5   | 10111                | 0000 0011                | 3   |

|                       |     | 11011                | 0000 0101                | 5   |

| 1111111               | 7   | 1011111              | 0000 0101                | 5   |

| 1111111               | /   | 1101111              | 0000 0111                | 7   |

| 11111111              | 9   | 101111111            | 0000 0111                | 7   |

|                       |     | 110111111            | 0000 1001                | 9   |

| 111111111             | 255 | 101111111            | 1111 1101                | 253 |

|                       | 233 | 11011111             | 1111 1111                | 255 |

Таблица 4 — Результаты моделирования обработки нарушений монотонности второго типа

| Правильная комбинация |   | Комбинация с ошибкой | Результат преобразования |   |

|-----------------------|---|----------------------|--------------------------|---|

| 11111                 | 5 | 10011                | 0000 0011                | 3 |

|                       |   | 11001                | 0000 0101                | 5 |

| 111111111 9           | 0 | 100111111            | 0000 0111                | 7 |

|                       | 9 | 110011111            | 0000 1001                | 9 |

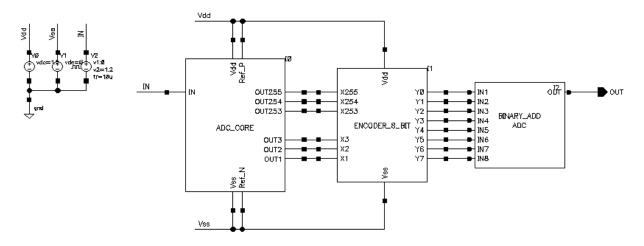

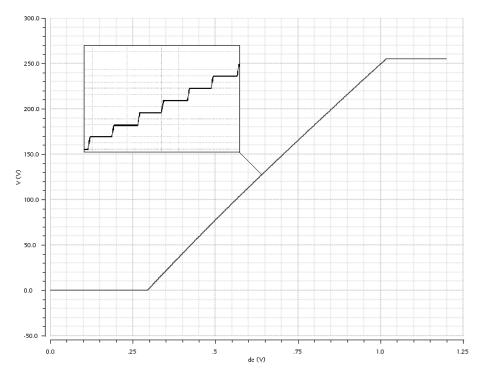

Моделирование характеристики преобразования восьмиразрядного параллельного аналого-цифрового преобразователя проводилось по схеме рисунка 17. Напряжение питания поступает на порт Vdd. Порт Vss присоединяется к земляной шине. Входной сигнал IN подается на аналоговую часть АЦП (блок ADC\_CORE), реализованную согласно рисунку 12. Термометрический код с выхода ADC\_CORE подается на цифровую часть АЦП (блок ENCODER\_8\_BIT), выполняющую преобразование в прямой двоичный код. Блок BINARY\_ADD осуществляет двоично-взвешенное суммирование сигналов с выходов Y0 — Y7. Результат моделирования характеристики преобразования представлен на рисунке 18.

Рисунок 17 – Схема моделирования АЦП

Рисунок 18 – Характеристика преобразования АЦП

Измерение интегральной (INL) и дифференциальной (DNL) нелинейностей проводятся по формулам (6) – (8), приведенным в [10]. При этом проводится определение порогов переключения компараторов, а затем выполняются вычисления по формулам (6) и (8), после чего вычисляется среднее значение параметра.

$$INL = \frac{\varepsilon(k)}{U_{\text{полн}}} \ 100 \% \tag{6}$$

где  $U_{\text{полн}}$  — диапазон входных напряжений АЦП,  $\varepsilon(k)$  — остаточное смещение k—го уровня опорного напряжения от идеального значения, вычисляемое из формулы (7):

$$\varepsilon(k) = Q(k-1) - T(k) + T_1 - U_{\text{CM HYJJS}}$$

(7)

где Q — расстояние между идеальными уровнями опорного напряжения; T(k)-k—ый уровень опорного напряжения рассматриваемого АЦП;  $T_1$  — идеальное значение первого уровня опорного напряжения;  $U_{\text{см нуля}}$  — напряжение смещения нуля характеристики преобразования АЦП.

$$DNL(k) = \frac{W(k) - Q}{Q} \tag{8}$$

где W(k) — расстояние между k+1 и k—ым уровнями опорного напряжения; Q — расстояние между идеальными уровнями опорного напряжения.

Эффективная разрядность определяется согласно [10] по формуле:

$$ENOB = N - log_2 \left( \frac{rms \, noise}{ideal \, rms \, quantization \, error} \right) \tag{9}$$

Результаты измерения интегральной и дифференциальной нелинейности и эффективной разрядности представлены в таблице 5. В таблице 6 приведено сравнение разработанной схемы в 90 нм КМОП технологии компании Angstrem-T с реализациями в 180 нм КМОП технологии компании UMC и 55 нм КМОП технологии компании Global Foundries. Из приведенного сравнения видно, что применение предложенных в работе решений при реализации параллельного аналого-цифрового преобразователя позволяет обеспечить малые потери в эффективной разрядности. Причем данное соотношение сохраняется при смене технологии.

Таблица 5 – Результаты измерений INL, DNL и ENOB

| Параметр  | Значение |

|-----------|----------|

| INL, бит  | 3,1      |

| DNL, бит  | 0,05     |

| ENOB, бит | 6,8      |

Таблица 6 – Сравнение с аналогами

| Параметр   | Значение |       |               |

|------------|----------|-------|---------------|

| Технология | UMC 180  | GF 55 | Angstrem-T 90 |

| INL, бит   | 2,2      | 2,5   | 3,1           |

| DNL, бит   | 0,03     | 0,05  | 0,05          |

| ENOB, бит  | 6,3      | 6,6   | 6,8           |

# Заключение

В рамках выполнения работы были достигнуты следующие результаты:

- Проведен обзор методов снижения потерь в эффективной разрядности;

- Разработана методика синтеза аналоговой часть параллельного аналого-цифрового преобразователя;

- Разработана методика синтеза цифровой части параллельного аналого-цифрового преобразователя;

- Синтезирован и промоделирован восьмиразрядный параллельный аналого-цифровой преобразователь по разработанной методике; результаты моделирования подтверждают работоспособность предложенной методики.

#### Список использованных источников

- 1. A. Zjajo, J. Pineda de Gyvez "Low Power High -Resolution Analog to Digital Converter. Design, Test and Calibration", Springer Science + Business Media B.V., 2011 315 p.

- 2. M. P. Flynn, C. Donovan, and L. Sattler, "Digital calibration incorporating redundancy of flash ADCs", IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., May 2003, vol. 50, no. 5, pp. 205–213.

- 3. A. Ismail, M. Elmasry, "A 6-bit 1.6 GS/s Low-Power Widdeband Flash ADC Converter in 0.13 μm CMOS Technology", IEEE J. Solid-State Circuits, Sept 2008, vol. 43, no 9, pp 1982 1990.

- 4. C. Sander, M. Clara, A. Santner, T. Harting, F. Kuttner, "A 6-bit 1.2 GS/s Low-Power Flash-ADC in 0.13- μm Digital CMOS", IEEE J. Solid-State Circuits, July 2005, vol. 40, no 7, pp 1499 1505.

- 5. M. P. Flynn, S. Park, Y. Palaskas, "A 4-Gs/s 4-bit Flash ADC in 0.18-μm CMOS", IEEE J. Solid-State Circuits, Sept 2007, vol. 42, no 9, pp 1865 1872.

- 6. J. Lee, J. Weiner, Y.-K. Chen, "A 20 GS/s 5-bit SiGe ADC for 40 Gb/s Coherent Optical Links", IEEE Trans. Circuits Syst. I, Reg. Papers., vol. 57, no. 10, pp. 2665-2674, Oct. 2010.

- 7. B. V. Hieu, S. Beak, S. Choi, J. Seon, T. T. Jeong, "Thermometer-to-binary Encoder with Bubble Error Correction (BEC) Circuit for Flash Analog-to-Digital Converter (FADC)", Communications and Electronics (ICCE), 2010 Third International Conference on, 11–13 Aug. 2010, pp. 102–106.

- 8. Д.О. Буданов, Д.В. Морозов, М.М. Пилипко, "Восьмиразрядный параллельный аналого-цифровой преобразователь с массивом избыточных компараторов" / Радиотехника и электроника. 2017. Т. 62. № 4. с. 399-410.

- 9. D. O. Budanov, M. M. Pilipko, D. V. Morozov, "Encoders For Flash Analog-to-Digital Converters" / 2018 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), pp. 173-177.

- 10. IEEE Standard 1241 for Terminology and Test Methods for Analog to Digital Converters, 2000.

# Список работ, опубликованных по теме научно-квалификационной работы (диссертации)

# Публикации в изданиях, рецензируемых ВАК

- 1. Д. В. Морозов, Д. О. Буданов, "Шифратор термометрического кода в прямой двоичной код" / Научно-технические ведомости СПбГПУ Информатика. Телекоммуникации. Управление, 1 (164), 2013, с. 87–92.

- 2. Д.О. Буданов, М.М. Пилипко, Д.В. Морозов, "Восьмиразрядный параллельный АЦП со сниженной дифференциальной нелинейностью" / Проблемы разработки перспективных микро- и наноэлектронных систем 2014. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2014. ч. III. с. 35-38.

- 3. D. O. Budanov, D. V. Morozov, M. M. Pilipko, "An 8-Bit Flash ADC With Reduced DNL" / Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2015. № 3. с. 10.

- 4. А. Коротков, Д. Морозов, М. Пилипко, И. Пятак, Д. Буданов, "Аналогоцифровые преобразователи для беспроводных систем связи: опыт разработки" / Электроника: Наука, технология, бизнес. 2016. № 2 (152). С. 40-47.

- 5. Д.О. Буданов, Д.В. Морозов, М.М. Пилипко, "Восьмиразрядный параллельный аналого-цифровой преобразователь с массивом избыточных компараторов" / Радиотехника и электроника. 2017. Т. 62. № 4. с. 399-410.

- 6. М.М. Пилипко, Д.В. Морозов, Д.О. Буданов, "Сравнительный анализ КМОП-схем шифраторов термометрического кода в прямой двоичный код для параллельных АЦП в интегральном исполнении" / Микроэлектроника. 2017. Т. 46. № 1. с. 50-60.

- 7. D. O. Budanov, M. M. Pilipko, D. V. Morozov, "Encoders For Flash Analog-to-Digital Converters" / 2018 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), January 29 February 1, 2018, St. Petersburg, Russia, pp. 173-177.

# Публикации в других изданиях

- 1. Д.О. Буданов, Д.В. Морозов, "Методы увеличения эффективной разрядности параллельных аналого-цифровых преобразователей" / В сб. материалов межвузовской научной конференции «ХL Неделя науки СПбГПУ» 5-10 декабря 2011 года, ч. ІХ, СПб.: СПбГПУ, 2011. с.44-46.

- 2. Д.О. Буданов, Д.В. Морозов, "Компаратор для параллельного АЦП" / В сб. материалов межвузовской научной конференции «XLI Неделя науки СПбГПУ» 3-8 декабря 2012 года, ч. IX, СПб.: СПбГПУ, 2012. с.33-35.

- 3. Д. О. Буданов, "Моделирование восьмиразрядного параллельного АЦП с массивом избыточных компараторов" / В сб. материалов X Международного научно-практического семинара «Проблемы современной аналоговой микросхемотехники», Шахты, 1-2 октября 2013 года, ч. І, Шахты: ИСОиП (филиал) ДГТУ, 2013, с. 69-72.

- 4. Д.О. Буданов, Д.В. Морозов, "Моделирование восьмиразрядного параллельного АЦП с учетом топологии кристалла" / В сб. материалов межвузовской научной конференции «Неделя науки СПбГПУ», 2-7 декабря 2013 года, ИФНиТ, ч. I, СПб.: СПбГПУ, 2014. с.137-139.

- 5. Д.О. Буданов, Д.В. Морозов, "Измерение характеристик аналогоцифровых преобразователей" / Научный форум с международным участием «Неделя науки СПбПУ» 1-6 декабря 2014 года, Институт физики, нанотехнологий и телекоммуникаций СПбПУ, СПб.: СПбПУ, 2015, с 148 -151.

- 6. Е. Л. Фертикова, Д. О. Буданов, "Шифраторы термометрического кода" / В сб.: Неделя науки СПбПУ материалы научного форума с международным участием. Институт физики, нанотехнологий и телекоммуникаций; В.Э. Гасумянц, Д.Д. Каров ответственные редакторы. 2015. с. 201-204.

- Е. Л. Фертикова, Д. О. Буданов, "Ошибки термометрического кода" / В 7. сб.: Неделя науки СПбПУ Материалы научной конференции c Институт физики, международным участием. нанотехнологий И телекоммуникаций. 2016. с. 118-120.

- 8. Е. Л. Фертикова, Д. О. Буданов, "Ошибки термометрического кода в параллельных АЦП" / В сб.: Неделя науки СПбПУ Материалы научной конференции с международным участием. Лучшие доклады. 2016. С. 106-110.

- 9. D. O. Budanov, D. V. Morozov, M. M. Pilipko, "An 8-bit Flash Analog-to-Digital Converter With An Array Of Redundant Comparators" / Journal of Communications Technology and Electronics. 2017. Vol. 62. № 4. pp. 421-431.

- 10. M. M. Pilipko, D. V. Morozov, D. O. Budanov, "Comparative Analysis Of CMOS Circuits Of A Thermometer-to-Binary Encoder For Integrated Flash Analog-to-Digital Converters" / Russian Microelectronics. 2017. Vol. 46. № 1. pp. 45-54.

| Аспирант _ |           | Буданов Дмитрий Олегович |

|------------|-----------|--------------------------|

|            | (подпись) |                          |